- •Министерство общего и профессионального образования российской федерации

- •Учебное пособие Воронеж 2000

- •Учебное издание

- •394026 Воронеж, Московский поспект, 14

- •1. Тестовое диагностирование в цифровой технике:

- •1.1. Введение

- •1.2. Тестовое диагностирование в цифровой технике: цепи и терминология

- •1.3. Процедуры и проблемы программного тестирования

- •1.4. Необходимость проектирования тестопригодных схем

- •2. Анализ тестопригодности: система camelot

- •2.1. Количественная оценка тестопригодности

- •2.2 Принципы вычисления управляемости

- •2.3 Принципы вычисления наблюдаемости

- •2.4 Принципы вычисления тестопригодности

- •2.4.1. Тестопригодность как функция управляемости и наблюдаемости

- •2.5. Применение системы camelot на практике.

- •2.5.1. Количественная оценка проектируемых схем.

- •2.5.2. Автоматический выбор контрольных точек.

- •2.5.3 Методика генерации тестов вручную.

- •2.5.4. Методика автоматической генерации тестов

- •2.6. О других системах анализа тестопригодности

- •2.7. Заключительные замечания о методах анализа

- •3. Методы структурного проектирования

- •3.1. Принцип метода сканирования: сканируемый путь

- •3.2. Сканирование с произвольным доступом

- •3.3. Метод сканирования, чувствительного к уровню тактового сигнала

- •3.4. Недостатки и достоинства методов сканирования

- •3.5. Методы самотестирования: bilbo

- •3.5.3. Устройство встроенного поблочного диагностирования логических схем (bilbo)

- •3.6. Заключительные замечания о методах сканирования

- •4. Генерация тестов для схем, реализующих принцип сканирования

- •4.1. Алгоритм podem, условные обозначения, понятия и принципы

- •4.1.5. Вычисление относительных значении управляемости

- •4.2. Процедура podem

- •4.2.1. Пример 1. Основной принцип podem

- •4.2.2. Пример 2. Многомерный d-проход

- •4.2.3. Пример 3. Переопределение состояний первичных входов

- •4.2.4. Заключение относительного алгоритма podem

- •4.3. Процедура raps

- •4.3.1 Пример 4. Процедура raps

- •4.3.2. Заключение о процедуре raps

- •4.4. Методика выполнения процедур raps и podem

- •4.4.1 Использование статического сжатия тестов

- •4.4.2. Использование динамического сжатия тестов

- •4.5. Замечание относительно процедуры моделирования неисправностей

- •4.6. Заключительные замечания о процедурах podem и raps

- •5. Практические рекомендации по проектированию тестопригодных схем

- •5.1. Средства поддержки процедуры генерации тестов

- •5.2. Средства поддержки процедур тестирования и поиска неисправностей

- •Содержание

4.6. Заключительные замечания о процедурах podem и raps

Задача генерации тестов для схем, реализующих метод сканирования пути, существенна только для их комбинационной части. Исследователи и программисты-диагносты уделяют этой проблеме значительное внимание, и выбор только одного алгоритма PODEM и посвящение целой главы его описанию может вызвать недоумение. Однако в действительности большинство алгоритмов генерации проверяющих тестов является лишь вариациями основного принципа активизации пути. В этом отношении алгоритм PODEM не отличается от многих других алгоритмов. Тем не менее, практическая эффективность этого алгоритма, соединенная с простотой подхода, является его отличительной особенностью. Но не только это. Следует учитывать, что алгоритм изначально разрабатывался для схем, реализующих принцип сканирования (в данном случае метод LSSD), и доказана его заметная эффективность для схем, содержащих до 50000 вентилей.

Именно по этим причинам алгоритм был выделен и подробно описан в этой книге. Тем не менее, это не должно препятствовать читателю при решении задачи генерации тестов для схем со сканированием применять и другие хорошо известные алгоритмы, такие, как D-алгоритм или алгоритм, основанный на активизации пути. Если уже программно реализованы другие алгоритмы генерации тестов и они работают удовлетворительно, то целесообразно их использовать. Если это не так, то рекомендуются описанные в данной главе процедуры PODEM и RAPS.

5. Практические рекомендации по проектированию тестопригодных схем

В этой главе представлено несколько практических рекомендаций, улучшающих тестопригодность цифровых схем или печатных плат. Многие из них продиктованы просто инженерной интуицией и были отмечены в предыдущих главах. Однако полезно собрать их вместе в едином перечне. Рекомендации подразделяются на два типа: те, которые направлены на упрощение процедуры генерации тестов, реализацию тестового диагностирования и поиск места неисправностей. (Трудно представить, что можно сделать для улучшения процедуры оценки эффективности тестов, за исключением одного очевидного, — обеспечить соответствующие инструментальные средства для поддержки процедуры моделирования.)

5.1. Средства поддержки процедуры генерации тестов

РЕКОМЕНДАЦИЯ 1

Максимизировать характеристики управляемости и наблюдаемости схемы

В настоящее время известно, что способность генерировать тесты и применять их существенно зависит от простоты или, иначе, способности управлять и наблюдать логические значения на внутренних узлах проверяемой схемы. На практике сделать это для каждого узла невозможно, однако существуют различные способы улучшения характеристик управляемости и наблюдаемости схемы. Эти способы являются предметом обсуждения в настоящем руководстве, и здесь будут рассмотрены два вопроса: к чему мы стремимся и как реализовать необходимые условия.

Отвечая на первый вопрос, рассмотрим управляемость. Узел считается управляемым, если тестер способен легко управлять любым логическим значением узла (0, 1 или третье состояние с высоким переходным сопротивлением). Аналогично узел считается наблюдаемым, если тестер способен легко наблюдать правильность логических значений узла. Если узлы схемы легко управляются и наблюдаются, то из этого следует, что внутренние логические элементы также будут легко управляться и наблюдаться. Примерами ключевых точек управления состояниями логической схемы являются.

а) входы тактовой синхронизации и сброса-установки устройств с памятью, таких, как триггеры, счетчики и сдвиговые регистры;

б) входы выборки данных в мультиплексорах и демультиплексорах;

в) шины управления третьим состоянием в устройствах с тремя устойчивыми состояниями выходов;

г) входы разрешения-захвата в микропроцессорах;

д) входы разрешение доступа и чтение-запись в элементах памяти;

с) шины управления, адреса и данных в любом устройстве.

Примерами ключевых точек наблюдения за состояньями логической схемы являются:

а) перечисленные выше шины управления, которые находятся внутри устройства и не имеют прямого доступа;

б) выходы устройств с элементами памяти, таких, как триггеры, счетчики и сдвиговые регистры;

в) выходы устройств, формирующих вспомогательные данные, таких, как генераторы четности, декодеры и мультиплексоры приоритета;

г) любой логически избыточный узел (обсуждается в дальнейшем в рекомендации 2);

д) магистральная часть узлов с большим числом ветвлений;

е) цепи глобальной обратной связи (обсуждаются в дальнейшем в рекомендации 7).

Ключевые точки управления и наблюдения в схеме могут быть определены с помощью либо приведенного перечня, либо системы CAMELOT (как описано в гл. 2), либо обоих способов одновременно.

После определения ключевых точек на следующем шаге необходимо модифицировать исходную схему для улучшения показателей управляемости и наблюдаемости. Общие методы улучшения доступа к внутренним точкам схемы показаны на рис. 5.1 и предусматривают использование:

а) незадействованных выводов кристалла или разъема печатной платы вместе с запасными логическими вентилями;

б) гнезд с двухрядным расположением выводов с перемещаемым контактным штепселем;

в) контрольных точек, размещенных на печатной плате (контактных столбиков);

Рис 5.1 Методы улучшения доступа к внутренним узлам схемы:

а – использование дополнительных входов и вентилей, б – разъем для корпусов типа DIP, в – контрольная точка, г – управление третьим состоянием, д – одно- и многоконтактная клипса

г) развязки с помощью элементов с тремя состояниями и дополнительными выводами-стойками для управления и наблюдения;

д) одно- и многоконтактных зажимов (клипс) для непосредственного подключения к выводам интегральных микросхем.

Согласно п. а) может быть также рассмотрено использование второго контактного разъема, расположенного с другой стороны печатной платы и обеспечивающего дополнительный доступ только для диагностического оборудования. Недостатком такого подхода является расширение средств интерфейса между печатной платой и диагностическим оборудованием (что противоречит рекомендации 19).

Заметим, что доступные точки схемы, такие, как контрольные точки и клипсы, можно использовать не только в качестве точек наблюдения, но и в качестве точек с ограниченным управлением с помощью подачи в узел сигнала, допустимого для физических элементов узла. В контрольной точке узла между двумя элементами серии ТТЛ может быть установлен низкий уровень (но не высокий), что позволяет частично управлять этим узлом. Метод иллюстрируется на рис. 5.2 и является практически полезным для управления потоком данных вдоль петли обратной связи.

Рис 5.2 Дополнительное управление через контрольные точки:

на узел Х через контрольною точку А подается 0. На узле Y устанавливается 1 (естественное состояние) или 0 (через контрольную точку В). Значение узла Х наблюдается через контрольную точку А (в узле через контрольную точку В может быть установлен 0)

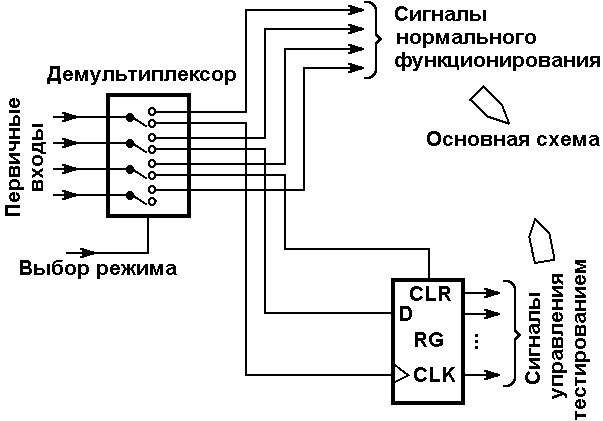

Если имеются ограничения на число первичных входов-выходов, то для улучшения параметров управляемости и наблюдаемости можно использовать мультиплексоры и демультиплексоры, как показано на рис 5.3. Заметим, что основные недостатки связаны с необходимостью использования дополнительных элементов и со снижением быстродействия из-за дополнительных задержек.

Рис 53 Использование мультиплексоров и демультиплексоров:

а — улучшение управляемости, б — улучшение наблюдаемости

Если доступ к внутренним точкам значительно ограничен, то для вывода информации из схемы вместо мультиплексоров, показанных на рис. 5.3,б, можно использовать генераторы четности. Свойство, присущее генератору четности, заключается в том, что сигнал на его выходе изменяется в результате изменения логического значения на одном из его входов. Если наблюдаемые контрольные точки выбраны определенным образом, то выходной сигнал генераторов четности можно использовать не только для обнаружения неисправностей, но также для определения места неисправного узла.

На рис. 5.4 показаны другие пути использования мультиплексоров, на этот раз для повышения значений управляемости и наблюдаемости на внутренних узлах с низким значением этих показателей.

Рис. 5.4. Улучшение значений управляемости (а) и наблюдаемости (б) узлов

Для улучшения доступа к внутренним точкам схемы подобные функции могут выполнять сдвиговые регистры, как показано на рис.5.5.

Рис 5.5. Использование сдвиговых регистров:

а – улучшение управляемости (последовательный ввод, параллельный выход); б –улучшение наблюдаемое и (параллельный ввод, последовательный вывод)

На рис. 5.5,а представлен сдвиговый регистр с последовательным вводом и параллельным выводом данных, который используется для установки определенного тестового состояния. (Иногда такой регистр называют регистров тест-состояния.) На рис. 5.5,б представлен регистр с параллельным выводом, используемый для сбора информации о состоянии схемы и последующего вывода информации через выход сканируемых данных. Существует некоторое подобие между этими структурами и более формальными структурами методов сканирования, описанных в гл. 3. Действительно, структуры на рис. 5.5 можно классифицировать как схемы, реализующие сканирование. Совместить две функции, реализуемые схемами на рис. 5.5, можно образовав структуру, известную под названием схемы сканирования-установки (рис. 5.6). Она содержит сдвиговый регистр с параллельным вводом-выводом данных и дополнительной функцией последовательного ввода-вывода путем сканирования данных.

Рис. 5.6. Реализация метода сканирования-установки

От более формальных методов сканирования, описанных в гл. 3, метод сканирования-установки отличается тем, что его схемная реализация может быть любой — как комбинационной, так и последовательной — и нет также ограничений на типы используемых элементов памяти и триггеров-защелок. Однако генерация эффективного множества тестов для основной схемы может быть сложной задачей.

Рис. 5.7. Использование демультиплексоров и сдвиговых регистров

На рис. 5.7 показано, как можно использовать совместно демультиплексоры и сдвиговые регистры в схемах с ограниченным доступом к внутренним точкам для передачи существенных тестовых сигналов управления узлами. Несомненно, существуют и другие решения, которые остаются за рамками обсуждения в расчете на изобретательность читателя.

В заключение, когда эта книга была подготовлена к печати, фирма AMD объявила о выпуске новой микросхемы Am 29818 последовательного теневого регистра. Эта микросхема содержит 8-разрядные операционный сдвиговый и теневой регистры. Теневой регистр либо загружается предварительно и независимо, либо загружается текущими данными, содержащимися в операционном регистре, и позволяет осуществить наблюдение за содержимым операционного регистра. Ввиду важности этой новой микросхемы и других выпускаемых следом за ней в приложение перепечатывается часть ее паспортных данных. Устройства, подобные рассмотренной микросхеме, дают, наконец, возможность разработчику схем на уровне печатных плат и системы использовать в полной мере методологию сканирования.

РЕКОМЕНДАЦИЯ 2

Исключать логическую избыточность

Узел схемы является логически избыточным, если все значения на выходе схемы не зависят от логического состояния узла на всех входных наборах и последовательности состояний.

Логическая избыточность часто вводится в схему либо преднамеренно, например, для исключения статических состязаний, либо случайно. Проблема, связанная с наличием логически избыточного узла, заключается в том, что, по определению, невозможно создать условия, при которых сигнал первичного выхода схемы зависел бы от состояния избыточного узла.

Это означает, что неисправности этого узла определенного типа не могут быть обнаружены. В результате появляются две проблемы. Первая заключается в том, что могут возникать условия состязаний, которые были устранены в исправной схеме; вторая проблема состоит в том, что избыточный узел может маскировать другую неисправность на неизбыточном узле схемы. Первый случай иллюстрируется на рис. 5.8.

Рис. 58 Необнаруживаемая неисправность, вызывающая появление состязаний

В этом примере для исключения возможных статических состязаний введен вентиль G3, который при переключении входного терма Х1Х2 на Х1Х2 реализует «связывающий» терм Х2ХЗ. Из выражения этой булевой функции следует, однако, что выход G3 логически избыточен. Поэтому невозможно создать условия транспортировки неисправности типа н-к-1 на выходе G3 через элемент G4. Условия установки на выходе G3 логического 0 противоречат требованиям установки 1 на выходах G1 и G2. Следовательно, активизированный путь через G4 не может быть установлен. Это означает, что схема будет функционировать правильно, но могут появиться условия для единичных статических состязаний (отрицательный импульс) на выходе G4, когда Х1-1 изменяется на XI = 0, а Х2=ХЗ=1. Длительность этого паразитного импульса определяется различием в путях распространения сигналов и может или не может быть достаточной, чтобы осуществить установку триггера. Следовательно, важно отметить, что непосредственное наблюдение за выходом G3 позволяет обнаружить неисправность н-к-1 этого выхода.

Вторая возможность состоит в том, что необнаруживаемая неисправность в избыточном узле может маскировать неисправность, которая обычно обнаруживается в исправной схеме. Пример, иллюстрирующий этот случай, приведен на рис. 5.9. Неисправность н-к-1 узла не обнаруживается на выходе Z ввиду несовместимых требований для значений входов XI, Х2, ХЗ.

Неисправность н-к-0 узла В обнаруживается на выходе входным тестовым набором XI =1, Х2=1, Х3=0. (Это единственный тест для этой неисправности.). Однако присутствие неисправности н-к-1 в узле исключает обнаружение неисправности н-к-0 в узле В.

Рис. 5.9. Маскирование неисправностей

РЕКОМЕНДАЦИЯ 3

Физически разделять аналоговые и цифровые схемы

Технические требования к средствам диагностирования и методология диагностирования для аналоговых и цифровых схем существенно различны. Эти два вида схем в процессе диагностирования необходимо физически разделять, несмотря на то, что они могут быть конструктивно расположены на одной и той же печатной плате или даже в одном и том же устройстве, как например, микросхемы кодеров-декодеров и цифровых фильтров. Это связано с тем, что из-за крутых фронтов цифровых сигналов могут возникать наводки на близко расположенных аналоговых шинах. Если появляется необходимость передачи цифровых сигналов вблизи аналоговых шин, то линии передачи цифровых сигналов должны быть тщательно рассчитаны и экранированы.

Для наблюдения сигналов, подаваемых на входы аналого-цифровых преобразователей удобно также иметь контрольные точки на входах преобразователей. Аналогично входные цифровые сигналы в цифро-аналоговых преобразователях желательно наблюдать в цифровой форме. Учитывая сказанное, аналоговые и цифровые подсхемы устройства следует проверить отдельно и, если необходимо, различным тестовым оборудованием.

РЕКОМЕНДАЦИЯ 4

Разбивать большие схемы на небольшие подсхемы для уменьшения затрат на процедуру генерации тестов

Приближенная оценка сложности процедур генерации тестов и моделирования неисправностей показывает, что для схем, реализованных на уровне печатной платы и содержащих n микросхем малой и средней степени интеграции, затраты на эти процедуры пропорционально величине между n2 и n3. Если схему можно разбить на две подсхемы (только для целей диагностирования), то затраты соответственно уменьшаются. Например, для n=100 при кубической зависимости затрат их сокращение в результате разбиения исходной схемы на две подсхемы, каждая из которых содержит 50 микросхем, составит

(503+503):(1003),

т. е. затраты сократятся приблизительно в семь раз по сравнению с таковыми в начальном варианте. Это сокращение становится даже более значительным, если схема модифицируется через некоторое время после выполнения диагностической программы для исходной схемы.

Логическое разбиение схемы должно быть основано на выделении ее распознаваемых подфункций и достигается с помощью введения дополнительных средств, позволяющих разделять эти подфункции, а также шины тактовой синхронизации, сброса и даже шины питания. В качестве альтернативы одна часть схемы может быть отделена логически от другой с помощью буферных элементов с тремя состояниями, управляемых элементов разрыва или мультиплексоров, как показано на рис. 5.10.

Рис. 5 10 Разбиение схемы на подсхемы:

а—использование переходных вентилей, б—использование мультиплексоров

Чтобы проиллюстрировать, как разбиение схемы помогает генерировать тестовые наборы, рассмотрим логическую схему полного одноразрядного сумматора SN7480, которая использовалась ранее в гл. 4 и приведена вновь на рис. 5.11. Схема разбивается естественным образом на четыре подсхемы SC1—SC4, как показано на рисунке. Рассмотрим теперь, как с учетом этого разбиения проверять схему.

Рис. 5.11. Логическая схема полного одноразрядного сумматора типа SN7480

А. Проверка исправности подсхемы SC1. Генерировать множество тестов для подсхемы SC1, предполагается, что узел G3.12 является се выходом. Обеспечить наблюдаемость значения G3.12 на выходе NCN1, установив CN=0 и G4.12=1 (т. е. В*=0). Множество проверяющих тестов, покрывающих все одиночные неисправности SC1 типа н-к-1, н-к-0, представляется в виде

A1 |

A2 |

A* |

AC |

CN |

В* |

NCN1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Б. Проверка исправности подсхемы SC2. По аналогии с SC1 проверяющими тестами SC2 являются

В1 |

В2 |

В* |

ВC |

CN |

А* |

NCN1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

В. Проверка исправности подсхемы SC3. Генерировать множество тестов, предполагая, что узлы G3.12, CN и G4.12 являются входами, а NCN1– наблюдаемый узел. Заметим, что на первичном входе CN и псевдоходах G3.12 и G4.12 могут быть установлены 0 или 1 отдельно и независимо. Необходимое множество проверяющих тестов представляется в виде

A1 |

A2 |

A* |

AC |

B1 |

B2 |

В* |

ВС |

G3.12 |

G4.12 |

CN |

NCN1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

– |

– |

0 |

– |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

– |

– |

0 |

– |

0 |

1 |

1 |

0 |

– |

– |

0 |

– |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

– |

– |

0 |

– |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

– |

– |

0 |

– |

– |

– |

0 |

– |

1 |

1 |

0 |

0 |

Г. Проверка исправности подсхемы SC4. Эта подсхема представляет один из наиболее интересных случаев, поскольку сигнал на псевдовходс G 12.12 сам является функцией сигналов трех других входов (G3.12, CN, G4.12). Это значит, что невозможно создать определенные комбинации значений на этих четырех входах. Читатель может проверить и убедиться в том, что следующее множество тестов покрывает все одиночные неисправности типа н-к-1, н-к-0, образуя проверяющий тест для SC4:

A1 |

A2 |

A* |

AC |

B1 |

B2 |

В* |

ВС |

G3.12 |

G4.12 |

CN |

G12.12 |

SUM |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

– |

– |

0 |

– |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

– |

– |

0 |

– |

0 |

1 |

1 |

0 |

0 |

– |

– |

0 |

– |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

– |

– |

0 |

– |

– |

– |

0 |

– |

1 |

1 |

1 |

0 |

1 |

Если даже не совмещать полученные тестовые наборы, то полное множество тестов, обнаруживающих все одиночные константные неисправности схемы, включают 24 теста. В сравнении с тривиальным исчерпывающим тестом, который содержит 29=512 тестовых наборов, полученное множество тестов предпочтительнее. Тот же вывод следует из сравнения с множеством из 48 тестов, требуемых для исчерпывающего тестирования каждой подсхемы

(48=24(для SC1)+24(для SC2)+23(для SC3) +23(для SC4))

Читателю предлагается решить подобную задачу для микросхемы арифметического логического устройства типа SN74181.

РЕКОМЕНДАЦИЯ 5

Избегать использования асинхронных логических схем

В асинхронных схемах используются элементы памяти (в форме асинхронных защелок) и цепи глобальной обратной связи, однако переходы состояний происходят исключительно под управлением изменения состояний первичных входов. Системная тактовая синхронизация, определяющая переход схемы из одного устойчивого состояния в другое, отсутствует.

Достоинством асинхронных схем является высокое быстродействие. Скорость перехода из одного состояния в другое ограничивается только временем задержки сигнала при прохождении через вентили и соединения схемы. В этом смысле разрабатывать асинхронные схемы труднее, чем синхронные (тактируемые), и необходимо относиться с должным вниманием к возможности появляется в схеме состязаний. Существуют методы проектирования асинхронных схем, исключающие состязания. Проблема состоит в том, что присутствие в схеме неисправности может привести к появлению состязаний.

Обеспечить тестовое диагностирование таких схем может оказаться весьма трудной задачей, особенно если результат состязаний не проявляется постоянно, когда создаются условия его проявления. Сложность тестирования таких схем не является единственной проблемой. Может вызывать затруднения при выполнении процедуры моделирования неисправностей возможность недетерминированного поведения схемы. В результате синхронная логика предпочтительнее асинхронной. Даже при решении вопроса о том, какой счетчик использовать в схеме, предпочтение отдается синхронным, а не асинхронным счетчиком со сквозным переносом или асинхронно связанным синхронным счетчикам.

Рис. 5 12 Установка начального состояния элементов памяти:

а—общий согласующий резистор (сброс и установка фиксируются высоким тронном через общий резистор; проблема в том, что если с целью установки тестер обеспечить в точке Х низкий уровень, то после снятия сигнала состояние триггера неопределенное); б — независимые согласующие резисторы (триггер может быть установлен в 1 или сброшен в 0 путем приложения к выводам PR и CLR сигнала низкого уровня: тестер должен быть снабжен перекидным щупом), в—реализация начальной установки триггера

РЕКОМЕНДАЦИЯ 6

Обеспечить простоту начальной установки элементов памяти схемы

Установка начального состояния обязательно предшествует любой практической тестовой программе и процедуре моделирования. В идеале должна существовать возможность установки каждого элемента памяти схемы в известное начальное состояние.

Иногда случается, что отдельные входы установки и сброса элементов памяти на печатных платах связаны с шиной питания через согласующий резистор. На рис. 5.12 иллюстрируются некоторые из этих проблем и их решения, удовлетворяющие требованиям начальной установки. Заметим, что «перевес» установочного сигнала тестера необходим не только для прямого управления входом CLR триггера, но и для проверки свойства самоустановки триггера при включении питания. Чрезвычайно неудобно также, если единственный способ установки триггера в начальное состояние может быть реализован путем отключения и последующего включения питающего напряжения и воздействия его через RC-цепь на установку состояния триггера. При установке в начальное состояние возникают и другие проблемы, когда состояние одного элемента памяти зависит от состояния другого, как, например, в счетчике с последовательным переносом. Если каждый триггер не управляется независимо от других, то начальная установка достигается только последовательной подачей тактовых импульсов, пока счетчик не установится в определенное состояние, которое идентифицируется тестером. Даже когда обеспечивается непосредственный доступ к входу RESET ведущего триггера разработчик, осуществляя установку, тем не менее может попасть в ловушку. На рис. 5.13 иллюстрируется одна такая ситуация. Читателю предлагается найти установочную последовательность, для которой действительно существует очень простая схема счетчика.

Задача: Установить счетчик в известное начальное состояние

Рис. 5.13. К вопросу о начальной установке счетчика

РЕКОМЕНДАЦИЯ 7

Обеспечить возможность разрыва цепей обратной связи

Нельзя не выделить важность этой возможности. Цепи глобальной обратной связи усложняют процедуры генерации тестов и моделирования неисправностей. Петли обратной связи могут разрываться и управляться различными способами, как показано на рис. 5.14.

Рис. 5.14. Способы разрыва и управления цепями обратной связи:

а – исходная схема; б – переключатель или разъем, установленный на плате; в – сигнал запрета тестера; г – управление третьим состоянием; д – тестовый сигнал

РЕКОМЕНДАЦИЯ 8

Избегать использования одновибраторов

Использование одновибраторов в логических схемах сопряжено с различными трудностями, которые встречаются при реализации тестового диагностирования.

Первая проблема состоит в том, что если необходимо измерить период срабатываний одновибратора, то следует обеспечить непосредственное наблюдение сигнала с выхода одновибратора. Если такой возможности нет, то в процессе диагностирования непосредственный доступ к выходу одновибратора осуществляется с помощью клипсы.

Вторая проблема заключается в том, что, даже если существует возможность непосредственно наблюдать сигнал на выходе одновибратора, может оказаться, что быстродействие тестера меньше периода срабатываний одновибратора. Эта проблема может быть решена либо путем использования защелок, улавливающих импульс одновибратора, либо путем увеличения длительности импульса одновибратора с помощью дополнительного внешнего конденсатора, подключаемого клипсой. Эти способы иллюстрируются на рис. 5.15.

Обратная задача связана с тем, что одновибратор может иметь очень длинный импульс (порядка микросекунд и даже секунд). Вопрос теперь в том, не как измерить его длительность, а каким образом укоротить ее так, чтобы сохранить приемлемым время тестирования. Это достигается путем подключения с помощью клипсы дополнительного резистора параллельно резистору одновибратора;

В заключение, если нельзя избежать использования одновибратора, необходимо обеспечить прямой доступ к линии сброса.

Рис. 5.15. Способы управления одновибраторами:

а – исходная схема; б – непосредственная наблюдаемость; в – триггер-защелка в состоянии 0; г – удлинение импульса с помощью включения внешнего конденсатора; д – замена сигналом тестера

РЕКОМЕНДАЦИЯ 9

Избегать разработок с предполагаемой «подгонкой» отдельных компонентов

Отдельные компоненты – это такие элементы схемы, которые отбираются в соответствии с существующей номенклатурой и настраиваются в соответствии с техническими требованиями для конкретной печатной платы. Эти процедуры имеют общие названия «отборочный контроль» и «подгоночный контроль» компонентов. Примерами могут служить многооборотные фиксируемые потенциометры или линии задержки с отводами. Проблема при этом состоит в том, что часто трудно установить стандартный проверяющий тест, или в том, что тест становится сложнее проверяющего теста при отсутствии таких компонентов. Например, тестовая программа может включать процедуру автоматического измерения фиксированной задержки, однако для измерения задержек, длительности которых меняются от платы к плате, вынуждены использовать программный цикл и осциллограф. Если схема проектируется для серийного производства, то всегда должна существовать возможность установки схемы в состояние, в котором она проверяется стандартным тестом. Это означает, что требования на разработку для серийного производства должны выполняться не с помощью необратимых изменений схемы, таких, как разрезание соединений или дорожек, а с помощью переключаемых регулировок, съемных контактных разъемов или перемычек на задней панели.

РЕКОМЕНДАЦИЯ 10

Избегать зависимости проверяющей программы от информации, записанной в ПЗУ и ПЛМ

Постоянные запоминающие устройства (ПЗУ) и программируемые логические матрицы (ПЛМ) часто используются вместо комбинационных схем, реализованных на типовых вентилях. С введением цепей обратной связи эти устройства позволяют также реализовать конкретную последовательностную схему. Однако для тестового диагностирования следует учитывать другие особенности их использования.

Первая состоит в том, что устройства могут не содержать определенных наборов из 0 и 1, необходимых для создания некоторого активизированного пути в какой-нибудь части схемы. Если это так, то при реализации тестирования необходимо иметь возможность установить на выходах устройства третье состояние (путем управления входом кристалла ENABLE — РАЗРЕШЕНИЕ ДОСТУПА) и затем с помощью клипсы обеспечить доступ к выводам микросхемы, как показано на рис. 5.16.

Рис 5 16 Способы управления входов ENABLE ПЗУ:

а – ПЗУ на плате, вход ENABLE заземлен; б – заземлен согласующий резистор; в – согласующий резистор подключен к источнику питания

На рис. 5.16,а вход разрешения доступа ENABLE непосредственно связан с корпусом, т. е. доступ в ПЗУ разрешен постоянно. Это означает, что тестер не может управлять входом. На рис. 5.16,6 и в показаны два способа организации доступа к этому входу. На рис. 5.16,6 вход подключен к шине 0 через согласующий резистор, в то время как на рис. 5.16,а вход подключается к источнику питания. Последняя схема в большей степени защищена от помех, но требует больших затрат. Управление входом ENABLE микросхемы и возможность установки клипсы важны и с другой точки зрения. Иногда информация, записанная в ПЗУ и ПЛМ, изменяется, когда модифицируется схема, реализуемая на печатной плате. Поэтому целесообразно ослабить зависимость программы проверки исправности от содержимого ПЗУ и ПЛМ для того, чтобы защитить существующую тестовую программу от возможных изменений.

РЕКОМЕНДАЦИЯ 11

Подключить нагрузку ко всем неиспользуемым входам устройств и к выходам устройств с открытым коллектором или с тремя состояниями

В соответствии с техническими требованиями к проектированию схем неиспользуемые входы логических устройств всегда необходимо подключать через согласующий резистор к шине питания или общей шине. Это делают для того, чтобы исключить воздействие шума на входы с плавающим уровнем логического состояния.

Подключение нагрузки к неиспользуемым входам имеет важное значение для процедуры тестирования, так как позволяет управлять поведением устройства (как обсуждалось в рекомендации 10). Кроме того, не менее важно, чтобы подключение нагрузочного резистора при диагностировании позволило формировать в этом узле высокий и низкий логические уровни.

Используемые и неиспользуемые выходы устройств с открытым коллектором и с высоким переходным сопротивлением должны также нагружаться через согласующие резисторы, чтобы исключить неопределенность логических значений, которая приводит к неустойчивости сигнатур, определяемых в узлах с помощью пробника.

Если система спроектирована так, что устройства, выходы которых соединяются общей шиной, расположены на различных печатных платах и соединяются между собой шиной на задней панели, то в общем случае выходы с высоким переходным сопротивлением каждой платы могут оказаться ненагруженными. (Блок нагрузочных резисторов обычно размещается на общей шине задней панели.) В этом случае, если в тестере существует возможность подключения выходов с высоким переходным сопротивлением к нагрузке, при проверке отдельной платы необходимо иметь специальный адаптер. Для исключения этого недостатка можно размещать нагрузочные резисторы шины на каждой плате. В режиме нормального функционирования все нагрузочные резисторы, кроме одного блока резисторов, должны быть отключены либо конструктивно-технологическим способом, либо с помощью выключателей на печатной плате.