- •Министерство общего и профессионального образования российской федерации

- •Учебное пособие Воронеж 2000

- •Учебное издание

- •394026 Воронеж, Московский поспект, 14

- •1. Тестовое диагностирование в цифровой технике:

- •1.1. Введение

- •1.2. Тестовое диагностирование в цифровой технике: цепи и терминология

- •1.3. Процедуры и проблемы программного тестирования

- •1.4. Необходимость проектирования тестопригодных схем

- •2. Анализ тестопригодности: система camelot

- •2.1. Количественная оценка тестопригодности

- •2.2 Принципы вычисления управляемости

- •2.3 Принципы вычисления наблюдаемости

- •2.4 Принципы вычисления тестопригодности

- •2.4.1. Тестопригодность как функция управляемости и наблюдаемости

- •2.5. Применение системы camelot на практике.

- •2.5.1. Количественная оценка проектируемых схем.

- •2.5.2. Автоматический выбор контрольных точек.

- •2.5.3 Методика генерации тестов вручную.

- •2.5.4. Методика автоматической генерации тестов

- •2.6. О других системах анализа тестопригодности

- •2.7. Заключительные замечания о методах анализа

- •3. Методы структурного проектирования

- •3.1. Принцип метода сканирования: сканируемый путь

- •3.2. Сканирование с произвольным доступом

- •3.3. Метод сканирования, чувствительного к уровню тактового сигнала

- •3.4. Недостатки и достоинства методов сканирования

- •3.5. Методы самотестирования: bilbo

- •3.5.3. Устройство встроенного поблочного диагностирования логических схем (bilbo)

- •3.6. Заключительные замечания о методах сканирования

- •4. Генерация тестов для схем, реализующих принцип сканирования

- •4.1. Алгоритм podem, условные обозначения, понятия и принципы

- •4.1.5. Вычисление относительных значении управляемости

- •4.2. Процедура podem

- •4.2.1. Пример 1. Основной принцип podem

- •4.2.2. Пример 2. Многомерный d-проход

- •4.2.3. Пример 3. Переопределение состояний первичных входов

- •4.2.4. Заключение относительного алгоритма podem

- •4.3. Процедура raps

- •4.3.1 Пример 4. Процедура raps

- •4.3.2. Заключение о процедуре raps

- •4.4. Методика выполнения процедур raps и podem

- •4.4.1 Использование статического сжатия тестов

- •4.4.2. Использование динамического сжатия тестов

- •4.5. Замечание относительно процедуры моделирования неисправностей

- •4.6. Заключительные замечания о процедурах podem и raps

- •5. Практические рекомендации по проектированию тестопригодных схем

- •5.1. Средства поддержки процедуры генерации тестов

- •5.2. Средства поддержки процедур тестирования и поиска неисправностей

- •Содержание

3.3. Метод сканирования, чувствительного к уровню тактового сигнала

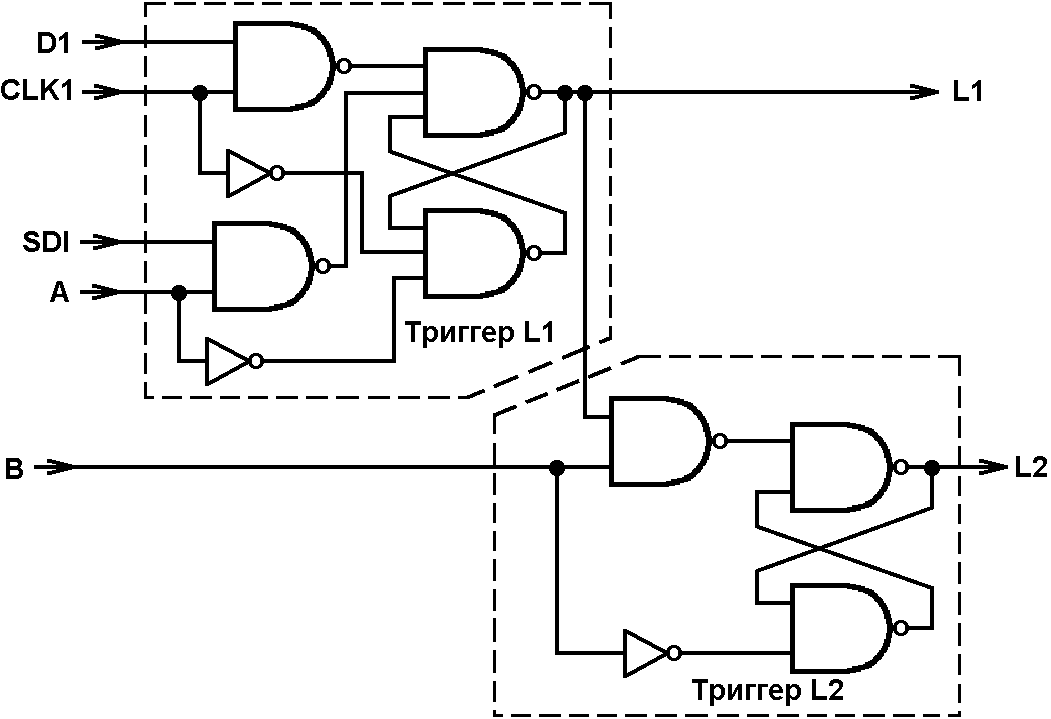

Рис. 3.7. Сдвигово-регистровый триггер-защелка, управляемый уровнем тактового сигнала

Существуют две основные особенности, характеризующие принцип проектирования схем на основе метода сканирования, чувствительного к уровню тактового сигнала (метод LSSD). Первая заключается в том, что состояния схемы изменяются под управлением уровня тактового сигнала, а не его фронта. Кроме того, установившееся состояние выхода как реакция на изменения значений состояний первичных входов не зависит от разброса задержек сигналов при распространении их через элементы схемы и ее внутренние соединения. Выходная реакция схемы не зависит также от порядка переключения входных переменных в случае одновременного изменения нескольких переменных. Это свойство «чувствительности к уровню» заложено с целью уменьшения зависимости схемы от ее изменяющихся параметров, таких, как время переключения элементов, задержки распространения сигналов или другие дефекты, которые могут создать условия для гонок или состязаний. Следовательно, в общем случае уменьшается влияние возможных физических дефектов, которые вызывают появление неисправностей динамического типа.

Вторая особенность метода LSSD заключается в том, что схема обладает свойством сканируемого пути. Это свойство обеспечивается применением специального элемента памяти, называемого «сдвигово-регистровым триггером-защелкой» (СРТ), управляемого уровнем тактового сигнала. Структурная схема такого элемента представлена на рис. 3.7, а его реализация на элементах И-НЕ на рис. 3.8.

Рис. 3.8. Реализация сдвигово-регистрового триггера-защелки на элементах И-НЕ

3.3.1. СДВИГОВО-РЕГИСТРОВЫЙ ТРИГГЕР-ЗАЩЕЛКА И МЕТОД LSSD

Сдвигово-регистровый триггер-защелка состоит из двух перекрестно-связанных (И-НЕ) триггеров - защелок L1 и L2. Триггер L1 представляет собой обычный элемент памяти с фиксацией состояния, имеющий входы для системных данных (D) и системного тактового сигнала (CLK) и выход для системных данных (L1). В режиме нормального функционирования на входы тактовых сигналов сканирования (А) и (В) подается логический 0. Фиксация состояния шины системных данных в триггере происходит в момент перехода системного тактового сигнала из 1 в 0.

Для функционирования сдвигово-регистрового триггера-защелки в режиме сканируемого пути тактовый сигнал сканирования А устанавливается в 1. Это позволяет состояние на входе сканируемых данных (SDI) записать непосредственно в триггер-защелку L1. Затем уровень тактового сигнала сканирования А возвращается в 0 (для фиксации состояния L1), а уровень тактового сигнала сканирования В устанавливается в 1. Это вызывает передачу информации, записанную в защелке L1, в триггер L2 с последующей фиксацией состояния L2 при переходе уровня тактового сигнала В из 1 в 0.

В реальных схемах LSSD сканируемый путь обеспечивается соединением триггеров-защелок в сдвиговый регистр в результате подключения выхода L2 (выход сканируемых данных) одного триггера к входу сканируемых данных другого триггера. Два тактовых сигнала А и В являются общими для всех триггеров-защелок. Один из вариантов реализации схемы методом LSSD на основе сдвигово-регистровых триггеров-защелок приведен на рис. 3.9. Подобная схема называется схемой на основе «двухступенчатого триггера-защелки».

Рис. 3.9. Реализация метода LSSD на основе двухступенчатого триггера-защелки

В такой структуре используется только выход L2 каждого триггера-защелки, а выход LI — не задействован. Выход L2 служит как выходом системных данных (значение переменных состояний Y), так и выходом сканируемых данных, который соединен с входом SDI следующей ячейки триггера-защелки. В результате каждая такая ячейка функционирует в режиме «ведущий—ведомый», причем передача данных в триггер осуществляется под управлением либо системного тактового сигнала и тактового сигнала сканирования (В) (в режиме нормального функционирования схемы), либо тактового сигнала сканирования А и следующего за ним тактового сигнала сканирования В (в режиме сканируемого пути). Поэтому в любом режиме работы гарантируется исключение состязаний. Название «двухступенчатый триггер» объясняется тем, что в любой его ячейке оба триггера образуют элемент памяти системы.

Другой вариант использования сдвигово-регистрового триггера-защелки при реализации метода LSSD, называемый структурой с одноступенчатым триггером-защелкой, показан на рис. 3.10.

В этой схеме выход L1 используется как выход внутренней переменной системы, а состязания сигналов исключаются путем разделения комбинационной части схемы на две отдельные части, обозначенные на рис. 3.10 как N1 и N2. Синхронизирующие входы N1 и N2 ячеек триггеров-защелок обозначены CLK1 и CLK2 соответственно. Выходы, связанные с N(1), являются входами внутренних переменных в N(2), и наоборот. Работой схемы управляют две системы тактовой синхронизации, CLK1 и CLK2, которые действуют таким образом, что в любой момент времени лишь один тактовый сигнал имеет высокий уровень, т. е. такты сигналов CLK1 и CLK2 не перекрываются. Таким образом исключается возможность состязаний сигналов. Название «одноступенчатый триггер-защелка» отражает тот факт, что только один триггер (L1) используется в качестве элемента памяти системы.

.

.

Рис. 3. 10. Реализация метода LSSD на основе одноступенчатого триггера-защелки

Основное различие между структурами с одно и двухступенчатыми триггерами-защелками заключается в быстродействии, с которым первичные выходы схемы реагируют на изменение сигналов на первичных и тактовых входах. В структуре с двухступенчатым триггером-защелкой требуется, чтобы два независимых и неперекрывающихся тактовых импульса (CLKA и В) были приложены, прежде чем изменение значений сигналов распространится через L1 и L2 и на первичных выходах комбинационной схемы N сформируется устойчивое значение сигнала как реакция на изменение входного воздействия. С другой стороны, в структуре с одноступенчатым триггером-защелкой соответствующие одиночные тактовые импульсы (CLK1 или CLK2), управляющие записью данных в L1, должны быть приложены, прежде чем установятся значения сигналов на выходах комбинационных схем (N2 и N1). В обоих случаях быстродействие определяется максимальным временем задержки распространения сигналов комбинационной частью схемы. Если эту задержку обозначить как N-задержку (mах), то максимальная длительность тактового импульса CLK для структуры с двухступенчатым триггером и CLK(l) или CLK2 для структуры с одноступенчатым триггером определится следующим образом:

CLK(max) < N-задержки (mах).

3.3.2. ИСПОЛЬЗОВАНИЕ ТРИГГЕРОВ-ЗАЩЕЛОК L1 И L2*

Недостаток структуры с одноступенчатым триггером-защелкой (см.рис.3.8) определяется тем, что триггер-защелка L2 в режиме нормального функционирования устройства не используется. В этом смысле он является избыточным и введение его для улучшения тестопригодности приводит к увеличению площади кристалла. Последний вариант ячейки триггера-защелки позволяет исключить этот недостаток путем организации более гибкой структуры схемы. Логическая схема такого триггера-защелки, называемого ячейкой L1/L2*, показана на рис. 3.11.

Основное отличие между основной ячейкой L1/L2 и модифицированной L1/L2* заключается в структуре триггера L2. Триггер-защелка L2* имеет дополнительный вход системных данных D(2), состояние которого фиксируется в триггере под управлением отдельного тактового сигнала CLK(2). Вход системных данных D2 на рис. 3.11 управляется системным тактовым сигналом, который в модифицированной схеме обозначен CLK1. Синхронизирующие импульсы CLK(l) и CLK(2) являются неперекрывающимися тактовыми сигналами. Возможности режима сканирования пути одинаковы в обоих схемах, а передача сканируемых данных, как и прежде, осуществляется под управлением тактовых сигналов сканирования А и В.

Рис. 3.11. Схема ячейки L1/L2* сдвигово-регистрового триггера-защелки

Триггер-защелка типа L1/L2* может использоваться в структуре одноступенчатым триггером таким образом, чтобы внутренние переменные схемы формировались как на выходе L1, так и на выходе L2. Эта возможность иллюстрируется рис. 3.12.

Рис. 3. 12. Реализация метода LSSD на основе одноступенчатого триггера-защелки типа L1/L2*

В этой схеме данные с выходов N1 подаются на входы D1 защелок L1, а данные с выходов N2—на выходы D2 защелок L2*. Таким образом, оба триггера-защелки, L1 и L2*, используются как элементы памяти в режиме нормального функционирования системы в отличие от структуры с одноступенчатыми триггерами на основе ячейки L1/L2. Заметим, что внутренние переменные системы, запитывающие входы ее комбинационной части N, поступают с выхода либо L1, либо L2*, но не с обоих одновременно (На рис. 3.12 показано, что выходные сигналы L1 используются как входные переменные N2, а выходные сигналы L2* как входные переменные N1.) Это ограничение вводится по двум причинам. Первая состоит в том, что при подаче обоих выходных сигналов L1 и L2* через цепи обратной связи на внутренние входы одной и той же комбинационной схемы исключается возможность реализации между L1 и L2* в каждой ячейке отношения «ведущий—ведомый» ввиду существования различных путей распространения сигналов через N1 и N2.

Второй причиной является отсутствие возможности установить в режиме тестирования требуемые тестовые наборы на выходах L1 и L2*. Это объясняется тем, что передача данных с выхода L1 на выход L2* и с выхода L2* в следующую защелку L1 осуществляется под управлением двух отдельных неперекрывающихся тактовых импульсов. Это означает, что либо значение сигнала на выходе L2* всегда соответствует значению L1, либо значение сигнала на выходе следующей защелки L1 всегда соответствует состоянию предыдущей L2*. Это накладывает ограничение на класс сканируемых последовательностей из чередующихся логических 0 и 1 и может привести к конфликтным ситуациям, как показано на рис. 3.13.

Рис. 3. 13. Пример нетестируемой схемы с одноступенчатыми триггерами-защелками:

набор 101 на входах вентилей G1 и G2 является тестовым; этот набор не может быть установлен на выходах двух триггеров-защелок LI, L2 *

3.3 3. ПРАВИЛА ПРОЕКТИРОВАНИЯ

В предыдущих подразделах были рассмотрены различные методы реализации принципа сканируемого пути на основе использования различных ячеек сдвигово-регистровых триггеров-защелок. Очевидно, существуют и другие варианты реализации, которые удовлетворяют требованиям внешних ограничений и дают простор искусству разработчиков схем. На практике, однако, такой метод проектирования, как LSSD, должен поддерживаться системой автоматизации проектирования, которая включает строгую проверку любых нарушений основных правил проектирования. Так называемая проверка соблюдения правил проектирования является основной особенностью метода LSSD, а эти правила описываются в данном подразделе. Некоторые из них очевидны сами по себе, другие введены для того, чтобы сохранить свойство чувствительности к уровню тактового сигнала или возможность сканирования данных. Вот эти правила.

Правило 1. Все элементы памяти должны быть типа сдвигово-регистрового триггера-защелки.

Правило 2. Триггер-защелка управляется двумя неперекрывающимися тактовыми импульсами таким образом, что:

а) выход L1 или L2 (L2*) ячейки 1 можно использовать для стробирования тактового импульса С, формируя стробируемый тактовый импульс С (G). Последний можно затем использовать для управления другой ячейкой 2 при условии, что ячейка 1 не управляется тактовым импульсом С;

б) при этом ограничении выходы ячейки 1 могут запитывать входы данных ячейки 2.

Правило 3. Должна существовать возможность идентификации множества тактовых сигналов ячеек триггеров-защелок, которые являются непосредственно управляемыми. Это означает, что:

а) все тактовые входные сигналы независимо друг от друга могут фиксироваться в пассивном состоянии;

б) любой единичный тактовый входной сигнал можно установить в активное состояние, в то время как другие поддерживаются в пассивном состоянии.

Правило 4. Первичные тактовые входы могут быть соединены только с тактовыми входами ячеек триггеров-защелок. Они не могут быть соединены с входами данных ячеек непосредственно или через комбинационную схему.

Проектирование с учетом правил 1—4 позволяет обеспечить схеме свойство чувствительности к уровню тактового сигнала. Следующие два правила обеспечивают возможность сканирования данных.

Правило 5. Все ячейки сдвигово-регистровых триггеров-защелок постоянно соединены так, что образуют один сквозной сдвиговый регистр, имеющий первичные вход и выход сканируемых данных и доступные тактовые входы, управляющие сканированием.

Правило 6. Должна существовать возможность реконфигурации структуры для ее работы в режиме сканирования путем непосредственного управления первичными входами таким способом, что:

а) все ячейки триггеров-защелок соединяются и образуют путь сканируемых данных;

б) все тактовые входные сигналы этих ячеек, за исключением тактовых сигналов сканирования А и В, могут быть переведены в пассивное состояние;

в) любой и каждый в отдельности вход сканирующего тактового сигнала А и В может быть переведен в активное состояние независимо друг от друга.

Говорят, что схемы, удовлетворяющие правилам 1—6, являются LSSD-схемами. Схемы с одноступенчатыми и двухступенчатыми триггерами-защелками, описанные выше, представляют простые примеры LSSD-схем. Несомненно, можно предложить более сложные схемы, удовлетворяющие в большей степени требования тестопригодности, однако конечная цель проектирования — сохранить простоту разрабатываемой структуры.