- •1. Автоматика и обобщенные характеристики элементов систем автоматики

- •Характеристики управления элементов сау

- •1.2. Основные параметры элементов

- •2. Генератор постоянного тока

- •3.1. Параметры управляемого вентиля-тиристора

- •3.2 Однополупериодные схемы выпрямления однофазного тока

- •3.3. Двухполупериодные схемы выпрямления однофазного тока

- •3.4. Трехфазная однотактная схема выпрямления тока (трехфазная схема со средней точкой, трехфазная нулевая трехпульсная схема)

- •3.5. Трехфазная двухтактная вентильная схема (схема Ларионова)

- •4. Инверторы

- •4.1. Однофазный инвертор со средней точкой

- •Входная и ограничительная характеристики инвертора. Зависимость входного постоянного напряжения (собственной противо эдс) от тока является входной характеристикой инвертора.

- •4.2. Инверторы напряжения

- •4.3. Инверторы тока

- •5. Составные многофазные схемы выпрямления

- •6. Узлы коммутации однооперационных тиристоров

- •8. Регуляторы переменного напряжения

- •8.1. Классификация регуляторов переменного напряжения

- •8.2. Тиристорные регуляторы напряжения переменного тока

- •8.3. Регуляторы с вольтодобавкой

- •8.4. Регуляторы с широтно-импульсным способом регулирования

- •8.5. Регуляторы с коэффициентом преобразования по напряжению больше единицы (повышающие и повышающе-понижающие регуляторы)

- •9. Преобразователи частоты

- •9.1. Непосредственные преобразователи частоты на вентилях с неполным управлением

- •9.2. Непосредственные преобразователи частоты на вентилях с полным управлением и циклическим методом формирования кривой выходного напряжения

- •9.3. Непосредственные преобразователи частоты с коэффициентом преобразования по напряжению больше единицы (повышающие циклоконверторы)

- •9.4. Спч с промежуточным звеном постоянного тока

- •10. Структурные схемы систем управления преобразовательных устройств

- •10.1. Системы управления выпрямителей и зависимых инверторов

- •10.2. Системы управления преобразователей частоты с непосредственной связью

- •10.3. Системы управления автономных инверторов

- •10.4. Системы управления регуляторов-стабилизаторов

- •11. Аналоговые регуляторы

- •12. Микропроцессорные системы в преобразовательной технике

- •13. Последовательностные цифровые устройства: триггеры, счетчики, память.

- •13.1. Триггеры

- •Контрольные вопросы и задания

- •13.2. Счетчики

- •14. Запоминающие устройства на основе интегральных микросхем

- •14.1. Интегральные микросхемы ис озу

- •14.2. Интегральные микросхемы ис пзу

- •9.1.1.1. Аналого-цифровые, цифро-аналоговые преобразователи

- •15.1. Аналого-цифровые преобразователи (ацп)

- •Параллельные ацп

- •Последовательные ацп

- •Последовательно-параллельные ацп

- •15.2. Цифро-аналоговые преобразователи

- •16. Датчики

- •16.1. Типы электрических датчиков

- •16.2. Структурные схемы датчиков

- •16.3. Потенциометрические датчики

- •16.4. Пьезоэлектрические датчики

- •16.5. Фотоэлектрические датчики

- •16.6. Радиотехнический датчик

- •16.7. Датчики температуры

- •16.8. Электромагнитные датчики

- •16. 9. Схемы усилителей для датчиков на основе оу

- •3.1. Параметры управляемого вентиля-тиристора 30

- •4.1. Однофазный инвертор со средней точкой 63

- •394026 Воронеж, Московский просп., 14

14. Запоминающие устройства на основе интегральных микросхем

14.1. Интегральные микросхемы ис озу

Адресные запоминающие устройства (ЗУ) подразделяются на RAM (Random Access Memory - память с произвольным доступом) и ROM (Read-Only Memory - память только для чтения). В отечественной литературе эти типы ЗУ называются соответственно Оперативным Запоминающим Устройством (ОЗУ) и Постоянным Запоминающим Устройством (ПЗУ). Первые, как правило, энергозависимы, а вторые, напротив - энергонезависимы. Среди ОЗУ различают устройства статические - Static RAM и динамические - Dynamic RAM (DRAM).

В ЗУ с произвольным доступом для хранения каждого бита информации используется отдельный элемент записи (ЭЗЭ). В зависимости от способа нахождения нужного элемента в массиве других однотипных элементов различают структуры с одномерной (линейной) и двумерной адресацией.

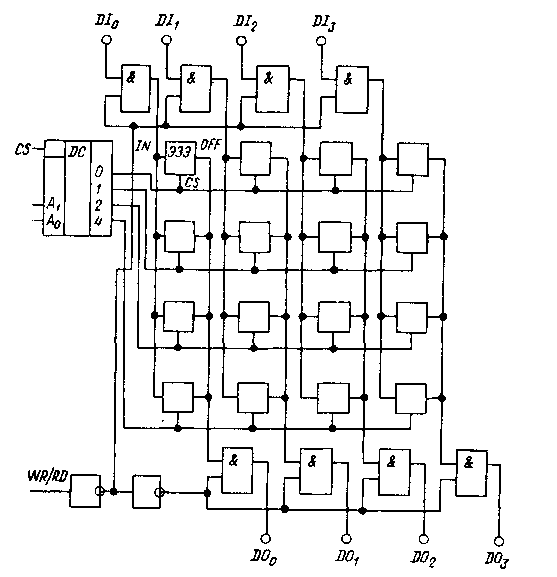

ЗУ с одномерной адресацией. На рис. 14.1 в качестве примера приведена структурная схема ЗУ (М=16, организация 4X4) с одномерной адресацией. Данная структура содержит матрицу 4X4 ЭЗЭ, каждый из которых, снабжен тремя выводами: входом информации (IN), выходом информации (OFF) и выходом разрешения работы — выбора кристалла (CS — chip select), дешифратор адреса, входные и выходные ключи на элементах 2И.

Если на вход дешифратора подано некоторое адресное слово, на соответствующем его выходе формируется сигнал лог. 1, который выбирает все ЭЗЭ, расположенные в одной из строк матрицы. Дальнейшая работа устройства зависит от того, какой режим работы задан управляющими сигналами. Если подан сигнал «чтение» (WR`/RD=1), то информация из выбранных ячеек подается на первые входы выходных элементов 2И. На вторые входы этих ключей подан единичный (пассивный) логический сигнал. Информация, хранившаяся в выбранных ЭЗЭ, попадает на выходные выводы DO0, DO1, DО2, DO3.

Если на схему подан сигнал «запись» (WR`/RD=0), то информация с входных шин DI0, DI1, DI2, DI3 через входные элементы 2И подается на входы ЭЗЭ и записывается в них.

Особенностью данной структурной схемы является одновременная запись и считывание информации, хранящейся в строке матрицы ЭЗЭ. Поэтому при заданной разрядности хранимого слова наращивание объема памяти может выполняться только за счет увеличения числа строк матрицы. Это, в свою очередь, ведет к значительному увеличению количества выходов дешифратора, т. е. к усложнению аппаратной реализации.

Рис. 14.1

С точки зрения упрощения дешифратора желательно выполнять матрицу ЭЗЭ прямоугольной. Однако при использовании рассмотренной структуры это предполагает увеличение разрядности выходного слова.

Решить это противоречие можно, если в качестве входных и выходных ключей ИС использовать соответственно схемы демультиплексоров и мультиплексоров. Применительно к ЗУ их принято называть селекторами. При этом часть разрядов адресного слова используется для управления селекторами.

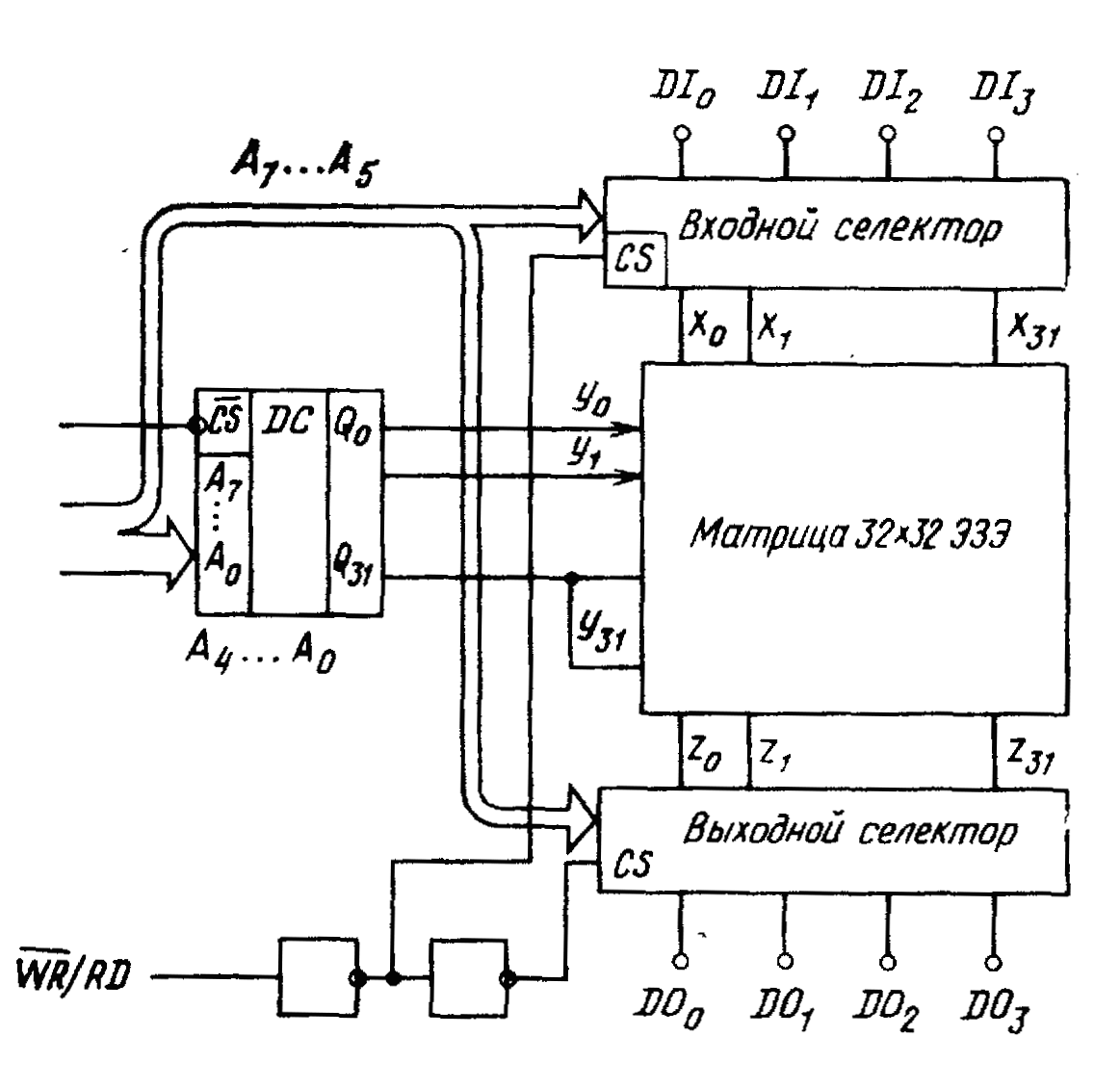

Структурная схема ЗУ с организацией 256X4, реализующая описанный принцип, показана на рис. 14.2. Она включает матрицу ЭЗЭ размером 32x32 элемента, дешифратор адреса, входной и выходной селекторы и элементы управления режимами чтения-записи. Каждый ЭЗЭ (см. рис. 14.2) снабжен тремя выводами: входом и выходом информации и выводом разрешения работы (выборки).

Рис. 14.2

Управление доступом к такому объему информации требует подачи на вход ЗУ 256 различных адресов, т. е. предполагает использование 8-разрядного адресного слова. Младшие его разряды (А4... А0), поступая на дешифратор адреса, выбирают из матрицы одну из 32 строк ЭЗЭ. При этом информация в зависимости от заданного режима работы может либо считываться (WR`/RD=1), либо записываться (WR`/RD = 0) во все элементы выбранной строки. Выбор нужных ЭЗЭ производится соответственно либо входным, либо выходным селекторами, которые в зависимости от значения старших разрядов адреса (А7... А5) выбирают из строки нужные элементы.

Очевидно, что описанные структуры выгодно использовать при одновременной записи-считывании информационных слов большой разрядности. В противном случае практическая реализация данных структур приводит к большим аппаратным затратам.

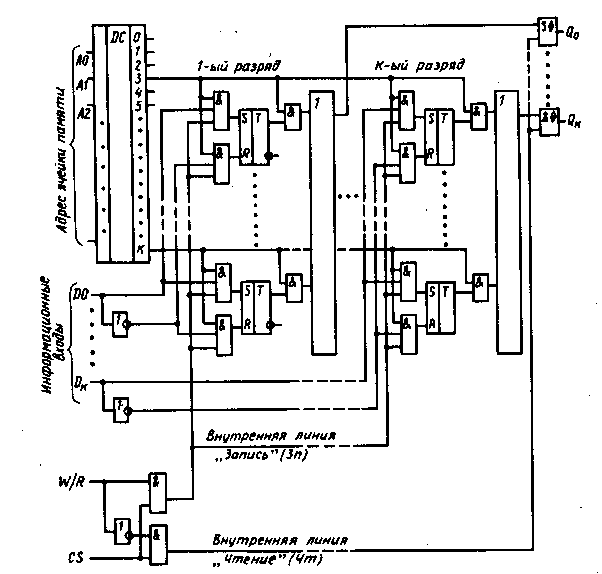

На рис. 14.3 показан один из вариантов управления внутренними элементами микросхемы сигнала.

Разряды ячейки матрицы составляют триггеры с входной и выходной логикой. Каждую ячейку — строку матрицы — выбирают с выхода дешифратора. Если СS=1 и W/R=1, то возбуждается линия «Запись» (Зп=1) и на входы S и R триггеров поступают взаимно инвертированные разряды записываемого слова с входов D0—D К. При этом на линии «Чтение» — логический 0, благодаря чему выходы Q0—QК трехстабильных элементов находятся в высокоомном состоянии: чтение информации с выходов триггеров исключено. Когда CS= 1 и W/R = 0 возбуждается линия «Чтение» (Чт= 1): занесенная в ячейку информация появляется на выходах Q0—Q К. Выходы триггеров в одноименных разрядах всех ячеек связаны с определенным дизъюнктором.

Рис. 14.3

Поэтому какая бы ячейка памяти ни была выбрана с выхода дешифратора, ее содержимое будет выведено на выходы Q0—QК . При возбуждении линии «Чтение» (W/R = 0) сигнал на линии «Запись» Зп = 0 — конъюнкторы на входах всех триггеров матрицы блокированы и запись с входов D0—DК осуществиться не может.

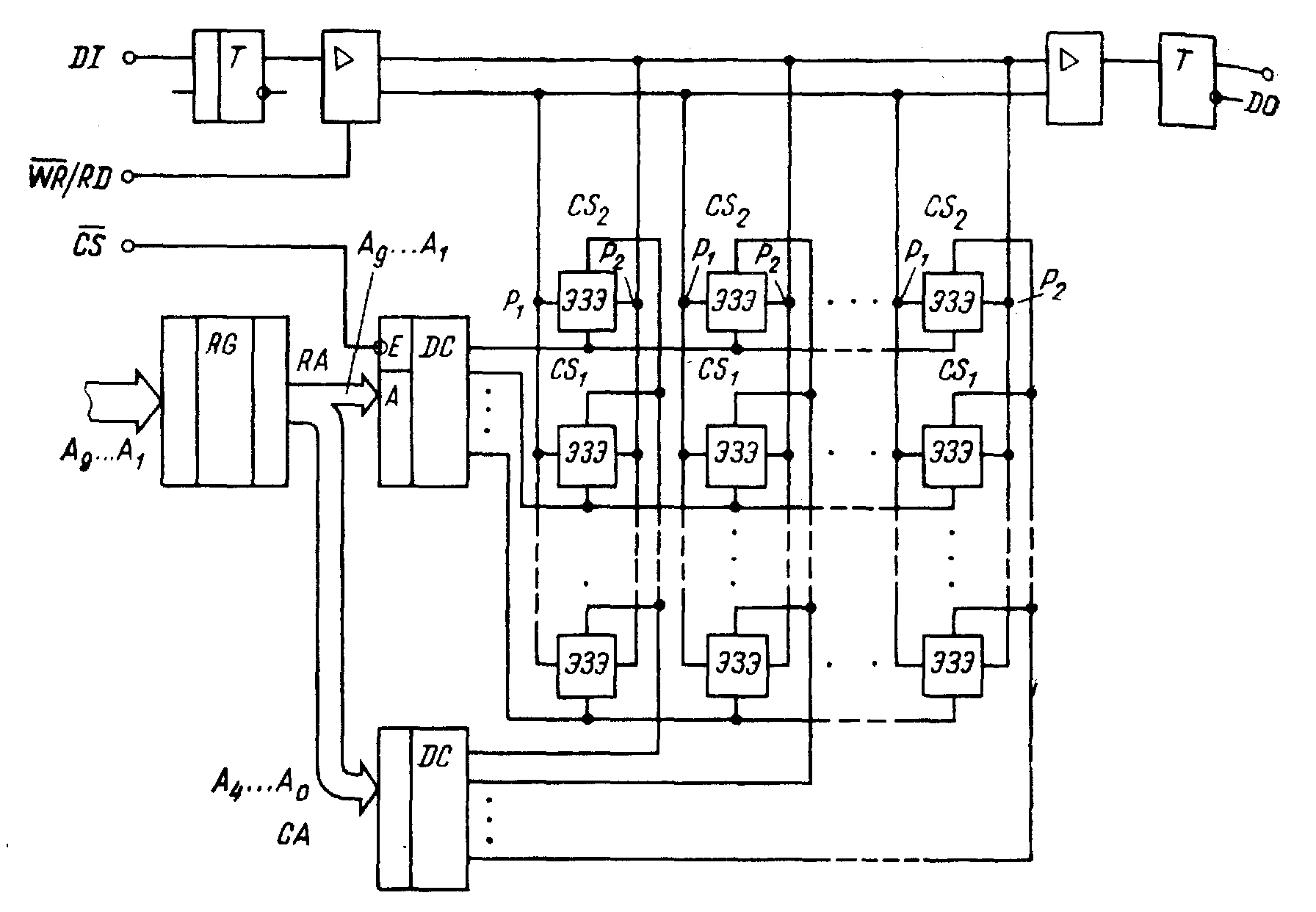

ЗУ с двумерной адресацией. При необходимости побитовой записи-считывания информации применяют структуру памяти с двумерной адресацией (рис. 14.4).

Данная структура содержит матрицу ЭЗЭ, статический регистр адреса, дешифраторы строки и столбца, усилители записи и считывания, входной и выходной буферные триггеры. Однако, в отличие от схемы рис. 14.3, каждый ЭЗЭ матрицы содержит не один, а два вывода разрешения работы (CS1 и CS2). При этом информационные выводы р1 и р2 являются обратимыми, т. е. позволяют как записывать так и считывать информацию. Для выбора нужной ячейки на оба входа CS необходимо подать активные логические уровни.

Цепи управления матрицей ЭЗЭ обеспечивают реализацию одного из трех режимов работы:

-хранения, при котором ЭЗЭ отключены от входа и выхода ИС;

-чтения, при котором информация из ЭЗЭ, выбранного по соответствующему адресу, выдается на выход ИС;

-записи, при которой информация со входа ИС записывается по указанному адресу.

Рис. 14.4

Каждому ЭЗЭ матрицы присваивается определенный адрес, поиск которого производится указанием номеров соответствующих строки и столбца. Эти номера формируются на выходах дешифраторов. Адрес ЭЗЭ в виде двоичного числа принимается по адресной шине регистром адреса. Число разрядов регистра адреса однозначно связано с объемом памяти ИС. Число строк и столбцов матрицы ЭЗЭ обычно выбирается равным целой степени числа 2, причем общий объем памяти определяется произведением числа трок (Nстр) на число столбцов Nстолб:

М = Nстр Nстолб= 2n12n2 = 2n1+n2 ,

где n=n1+n2 — число разрядов регистра адреса. Допустим, как и в схеме (рис. 2), M = 210=1024 (1 К). Однако, так как в этом случае организация памяти l K x l, то для доступа ко всей хранящейся информации необходимо 10-разрядное адресное слово (А9...А0), т. е. n=10. Если выбрать n1 =n2 = 5, то число строк и столбцов будет равно 32 и матрица ЭЗЭ будет квадратной.

Разряды регистра адреса делятся на две группы: одна (n1) определяет двоичный адрес строки (RA), другая (п2) —двоичный адрес столбца (СА). Каждая группа разрядов адреса подается на соответствующий дешифратор (строк и столбца). Выходные сигналы дешифраторов выбирают требуемый ЭЗЭ из матрицы.

При чтении (WR/RD = 1) содержимое этой ячейки через усилитель считывания выводится в выходной триггер.

Режим записи устанавливается путем подачи в усилитель записи сигнала разрешения записи (WR`/RD = 0). Этот сигнал открывает усилитель записи, и бит входной информации поступает на внутреннюю шину ИС, с которой переписывается в выбранный по соответствующему адресу ЭЗЭ.

Указанные процессы считывания-записи могут осуществляться только в случае, если на вход CS, соединенный с входом стробирования дешифратора строки, подан разрешающий сигнал. Обычно это сигнал лог. 0. При отсутствии этого сигнала работа дешифратора строки блокируется, что эквивалентно запрещению выборки ЭЗЭ по указанному адресу. В этом случае ИС находится в режиме хранения информации и ее выходы отключены от матрицы ЭЗЭ.

Рассмотренная организация памяти обеспечивает хранение 2n x1 кодовых слов, т. е. заданному адресу соответствует один бит информации. Использование метода двумерной адресации позволяет максимально упростить схему ИС, что при заданной площади кристалла является предпосылкой получения максимально больших объемов памяти.

Как уже отмечали, статическое полупроводниковое ЗУ состоит из элементов памяти (триггеров) на биполярных или МОП- транзисторах.

На рис. 14.5,6 приведены два примера элементов ЗУ, один из которых построен на биполярных транзисторах, а другой - на n-МОП-транзисторах. Статические ЭЗЭ, использующие биполярные транзисторы, это дорогостоящие устройства, выполненные на основе различных триггерных элементов. Данный класс схем обладает на сегодняшний день максимальным быстродействием.

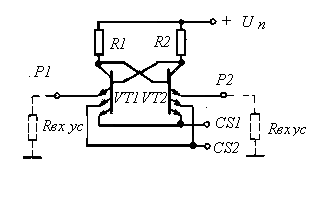

На рис. 14.5 приведена принципиальная электрическая схема ЭЗЭ на биполярных транзисторах. Данный элемент использует технологию ТТЛ и предназначен для применения в ЗУ с двумерной адресацией. Его основу составляют два инвертора, выполненных на трехэмиттерных транзисторах VTI и VT2. Инверторы включены последовательно и охвачены глубокой ПОС. Две пары попарно объединенных эмиттеров транзисторов образуют вывод выборки элемента CSI и CS2. Третья пара эмиттеров транзисторов образует прямой Р1 и инверсный Р2 выходы элемента, которые через входные сопротивления усилителя считывания подключены к общей шине.

Рис. 14.5

В режиме хранения на один или оба вывода выборки (CSI, CS2) ЭЗЭ подано напряжение низкого уровня. При этом триггер, образованный инверторами, находится в одном из устойчивых состояний. Предположим, что транзистор VT1 насыщен, a VT2 заперт. Весь ток насыщенного транзистора VTI замыкается через один; из выводов выборки элемента на общую шину. Поэтому в цепи выходного вывода Р1 ток отсутствует и информация из ЭЗЭ не попадает на вход усилителя считывания (UR вх ус =0).

Для считывания информации на оба входа выборки элемента необходимо подать напряжение высокого уровня. При этом единственным путем протекания тока насыщенного транзистора остается выходной вывод Р1 ЭЗЭ. Этот ток создает на входном сопротивлении усилителя считывания напряжение URвх ус, полярность которого соответствует записанной в элемент информации. Следует отметить, что при считывании из элемента информации она не теряется. При подаче на один или оба входа выборки напряжения низкого уровня триггер продолжает оставаться в том же состоянии.

При необходимости записать в элемент новую информацию на него также первоначально подаются сигналы выборки. После чего на внешних шинах устанавливается полярность напряжения, соответствующая новой информации. Для рассматриваемого случая на вывод Р1 подается напряжение высокого уровня, а на Р2 — низкого уровня. При этом так как все цепи протекания эмиттерного тока транзистора VT1 оказываются разорванными, на его коллекторе формируется напряжение высокого уровня. Это напряжение насыщает транзистор VT2, который, формируя на своем коллекторе напряжение низкого уровня, подтверждает запертое состояние транзистора VT1. В ЭЗЭ записывается новая информация. После снятия с элемента сигналов выборки новая информация будет храниться в триггере до момента очередной перезаписи. Таким образом, запись новой информации в рассматриваемый ЭЗЭ выполняется высоким уровнем входного напряжения. Если из многоэмиттерных транзисторов элемента исключить по одному эмиттеру, получим элемент для ЗУ с одномерной адресацией.

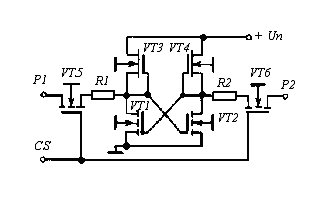

Применение в ЭЗЭ статических ОЗУ полевых транзисторов позволяет получить более высокую степень упаковки элементов, уменьшить стоимость и потребляемую мощность. Однако при этом быстродействие ОЗУ снижается. Построение ЭЗЭ статических ОЗУ на полевых транзисторах рассмотрим на примере элемента с одномерной адресацией. Его принципиальная электрическая схема приведена на рис. 14.6. Он также содержит два инвертора, но выполненных на основе ключей с нагрузочным МДП-транзистором.

Рис. 14.6

За счет введения цепи ПОС инверторы образуют структуру триггера. Выходы этого триггера через попарно последовательно включенные ограничительные резисторы R1 и R2 и транзисторы VT5 и VT6 соединены с выходными выводами Р1 и Р2 ЭЗЭ. Объединенные затворы транзисторов VT5 и VT6 образуют вывод выборки элемента CS.

Допустим, что в некоторый момент времени транзистор VT1 включен, а транзистор VT2 заперт. Если на вход выборки подано напряжение, недостаточное для отпирания транзисторов VT5 и VT6, триггер фактически отключен от выходных выводов P1 и Р2 ЭЗЭ, и информация на этих выводах отсутствует. ЭЗЭ находится в режиме хранения. Очевидно, что это состояние может длиться сколь угодно долго.