- •Роль микропроцессорной техники в мехатронных устройствах.

- •Способы представления двоичного кода в электронных устройствах.

- •История развития микропроцессоров.

- •Основные понятия. Микропроцессор, физическая и логическая организация, архитектура.

- •Основные типы архитектур. Неймановская и гарвардская архитектура.

- •Основные понятия. Программа, команда, объектный код, мнемокод.

- •Командный цикл. Фазы командного цикла.

- •Структурная схема микро-эвм на базе микропроцессора.

- •Регистры данных микропроцессора.

- •Регистры адреса микропроцессора.

- •Специальные регистры микропроцессора. Флаги, генерируемые микропроцессором

- •Регистры общего назначения микропроцессора.

- •Счетчик команд микропроцессора. Работа счетчика команд.

- •Понятие стека, назначение и организация.

- •Указатель стека микропроцессора. Работа указателя стека.

- •Классификация микропроцессоров по числу бис в комплекте и по разрядности.

- •Классификация микропроцессоров по назначению и виду обрабатываемых сигналов.

- •Классификация микропроцессоров по характеру временной организации работы и по количеству выполняемых программ

- •Особенности программного обеспечения микропроцессорных систем. Понятие транслятора. Виды трансляторов.

- •Языки Ассемблера. Номенклатура, характеристики

- •Элементы языка ассемблера для 8-ми разрядного микропроцессора.

- •Директивы языка ассемблера. Пример программы на языке ассемблера.

- •Преимущества применения однокристальных микропроцессоров при проектировании электронных измерительных устройств.

- •Состав регистров однокристального микропроцессора к1816ве48.

- •Банки рабочих регистров микропроцессора к1816ве48. Назначение и особенности.

- •Счетчик команд, указатель стека и регистр psw микропроцессора к1816ве48.

- •Флаги признаков микропроцессора к1816ве48

- •Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти данных dseg.

- •Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти программ cseg.

- •Организация памяти микропроцессора к1816ве48. Пространство внешней памяти данных xseg.

- •Система ввода-вывода микропроцессора к1816ве48. Порты ввода-вывода.

- •Службы реального времени микропроцессора к1816ве48. Таймер-счетчик: организация, возможности, программирование.

- •Службы реального времени микропроцессора к1816ве48. Система прерываний от внешнего источника запросов.

- •Службы реального времени микропроцессора к1816ве48. Система прерываний от таймера.

- •Генератор тактовых импульсов микропроцессора к1816ве48.

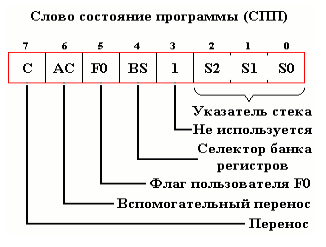

Флаги признаков микропроцессора к1816ве48

В состав АЛУ входят следующие блоки: комбинационная схема обработки байтов, регистры Т, регистр-аккумулятор А, схема десятичного корректора и схема формирования признаков. Аккумулятор используется в качестве регистра операнда и регистра результата. Регистр временного хранения операнда Т1 программно недоступен и используется для временного хранения второго операнда при выполнении двухоперандных команд. Комбинационная схема АЛУ может выполнять следующие операции: сложение байтов с переносом или без него; логические операции И, ИЛИ и исключающее ИЛИ; инкремент, декремент, инверсию, циклический сдвиг влево, вправо через (или минуя) флаг переноса, обмен тетрад в байте; десятичную коррекцию содержимого аккумулятора.

При выполнении операций обработки данных в АЛУ вырабатываются флаги (признаки), которые (за исключением флага переноса С) формируются на комбинационной схеме и не фиксируются на триггерах. К таким флагам относятся флаг нулевою содержимого аккумулятора и флаг наличия единицы в селектируемом бите аккумулятора. Логика условных переходов по указанным флагам позволяет выполнять команды передачи управления (JZ, JNZ, JB0 - JB7) без их фиксации на триггерах.

Флаги переноса и вспомогательного переноса (перенос из младшей тетрады в старшую) фиксируются на триггерах, входящих в состав регистра слова состояния программы (ССП).

Формат ССП показан на рисунке 3. Кроме

перечисленных признаков логика условных

переходов МК оперирует флагами FO и FI,

функциональное назначение которых

определяется разработчиком; флагом

прерывания от счетчика TF, сигналами на

входах Т0 и Т1, флагом внешнего прерывания

XF. Программистом могут быть также

использованы флаги рабочего банка

регистров BS и выбранного банка внешней

памяти программ МВ. Кроме того, логикой

переходов после окончания каждого

машинного цикла опрашивается еще два

флага, а именно флаг разрешения/запрета

прерываний от таймера ЕТ и внешних

прерываний ЕХ.

Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти данных dseg.

Пространство

внутренней

памяти данных

DSEG содержит

256 байт,

адресуемых

косвенно через

два адресных регистра R0, R1 выбранного

в данный момент регистрового банка. В

архитектуре

отсутствует прямой способ адресации

памяти, что привело к коротким однобайтовым

форматам команд

пересылки и

обработки, за

исключением

команд с

непосредственными

данными.Физическая

оперативная

память

однокристальных

МК, как

правило, не

покрывает всего

пространства

внутренней памяти данных из-за

нехватки площади кристалла. Так, в

приборах INTEL 8048 только

первые 64 байта покрыты физическим

ОЗУ. С усовершенствованием интегральной

технологии ожидается

увеличение объемов внутреннего

физического ОЗУ МК и его постепенное

приближение к

потенциальному барьеру 256 байт. Например,

в однокристальном МК ВЕ49, имеющем такую

же базовую

архитектуру,

что и

INTEL 8048,

объем физического

ОЗУ на

кристалле

увеличен до

128 байт,

а в 8050 все пространство в 256 байт

покрыто физическим ОЗУ. Особенностью

архитектуры INTEL

8048 является совмещение обоих банков

рабочих регистров и системного стека

с пространством

внутренней памяти данных, что дает

возможность рассматривать хранящиеся

в них объекты с двух

сторон. Структура наложения

представлена на рис. Слова в памяти

данных располагаются в двух

соседних байтах. В байте с младшим

адресом хранится младшая часть слова,

его адрес является

адресом всего слова. Такая форма

хранения слов соответствует типовой.

Возможен единственный

способ адресации

внутренней

памяти д анных

— косвенный

регистровый по

R0 или

R1.

анных

— косвенный

регистровый по

R0 или

R1.

Пространство DSEG включает в себя 256 ячеек памяти, часть из которых является одновременно элементами других пространств (Рис.5.13). Так, первые 32 байта ОЗУ занимают 4 банка РОНов. Служебные регистры, порты ввода/вывода, таймеры, аккумуляторы и др. так же совмещены с ячейками памяти и полями битового сегмента. Это дает возможность обращения к одному физическому объекту разными способами. Так, к ячейке DSEG[E0] можно обратиться по прямому и косвенному адресу, обратиться как к аккумулятору A и как к полю BSEG[E0..E7] (к каждому биту в отдельности).

Адресация к каждому отдельному биту

пространства BSEG (строка 2 пространства

DSEG) показана ниже.