- •Воронеж 2014

- •Введение

- •Основные сведения из физики твердого тела

- •1.2. Терминология и основные понятия

- •1.3. Статистика электронов и дырок в полупроводниках

- •1.3.1. Распределение квантовых состояний в зонах

- •1.3.2. Концентрация носителей заряда и положение уровня Ферми

- •1.4. Концентрация электронов и дырок в собственном полупроводнике

- •1.5. Концентрация электронов и дырок в примесном полупроводнике

- •1.6. Определение положения уровня Ферми

- •1.7. Проводимость полупроводников

- •1.8. Токи в полупроводниках

- •1.9. Неравновесные носители

- •1.10. Уравнение непрерывности

- •2. Электронные устройства систем промышленной электроники

- •Аналого-цифровые и цифро-аналоговые преобразователи Принцип аналого-цифрового преобразования

- •Принцип действия цифро-аналогового преобразования

- •Компараторы

- •Заключение

- •Библиографический список

- •Твердотельная электроника

- •В авторской редакции

- •394026 Воронеж, Московский просп., 14

2. Электронные устройства систем промышленной электроники

2.1. Аналоговые устройства

2.1.1. Транзисторные усилители электрических сигналов

В современной технике при решении многих инженерных задач возникает необходимость в усилении слабых электрических сигналов, что осуществляется электронными усилителями. Электронным усилителем называют устройство, предназначенное для усиления напряжения, тока и мощности электрических сигналов.

В настоящее время в электронных усилителях используются биполярные и полевые транзисторы. Исследуемые в данной работе электронные транзисторные усилители являются основными видами усилителей как на дискретных элементах, так и в интегральных микросхемах.

Усилители на биполярных транзисторах. Одним из наиболее распространенных усилителей на биполярных транзисторах является усилитель с общим эмиттером (ОЭ). В этом усилителе (рис. 2.1,

а) эмиттер является общим электродом для входной и выходной цепей. Входное напряжение Vвх от источника усиливаемого сигнала подается на усилительный каскад через конденсатор связи Сс1.

Усиленное выходное напряжение может быть снято как с резистора Rк, так и с транзистора, поскольку переменные составляющие этих напряжений равны (но противофазны). Однако, на практике выходное напряжение удобно снимать с транзистора, так как в усилителях с ОЭ эмиттер заземляется и выходное напряжение снимается между заземленной точкой корпуса (землей) и коллектором транзистора. В этом случае вход и выход усилителя имеют общую точку (земля). Если выходное напряжение снимать с резистора Rк, то общей точки между входом и выходом усилителя не будет, что вызывает большие неудобства, поскольку анализ работы и измерения ведут относительно «земли».

Анализ работы усилителя с ОЭ удобно проводить с помощью вольт-амперных характеристик транзистора (рис. 2.2.): входной характеристики IБ=f(VБ) на рис. 2.2. она повернута на угол 90) и семейства выходных характеристик Iк=f(Vк) при разных токах базы. Для коллекторной цепи усилителя (рис. 2.1, б) в соответствии со вторым законом Кирхгофа можно записать Vк=Eк–RкIк. Графическое решение этого уравнения показано на рис.2.2.

Прямая MN, называемая линией нагрузки, построена по двум точкам, соответствующим режиму холостого хода и короткого замыкания (координаты точки N: Vк=Eк, Iк=0; координаты точки М: Vк=0, Iк= Eк/Rк. Точки пересечения линии нагрузки с выходными характеристиками транзистора определяют ток Iк и напряжение на транзисторе Vк при любом заданном значении тока базы IБ

Сопротивление резистора Rк выбирают исходя из требуемого усиления входных сигналов. Но при этом надо иметь в виду, чтобы линия нагрузки проходила левее и ниже допустимых значений Vк max, Iк max, Pк max и обеспечивался достаточно протяженный линейный участок переходной характеристики. С целью выполнения этих требований сопротивление Rк должно составлять 0,2—5 кОм для транзисторов малой мощности и 100 Ом для транзисторов средней мощности.

Переходная и передаточная характеристика усилителя Iк=f(IБ) построена по точкам пересечения линии нагрузки с выходными характеристиками транзистора. Из рис. 2.2. видно, что передаточная характеристика нелинейная, но на ней можно выделить линейный участок ab. В усилителе действуют два источника: источник постоянной ЭДС Eк и источник усиливаемого переменного напряжения eвх.

Анализ работы любого усилителя следует начинать с режима покоя, т.е. при Vвх=0. Резистор RБ, включенный в цепь базы, обеспечивает требуемый режим покоя, который на характеристиках рис. 2.2 определяется точкой n, называемой рабочей точкой.

Для усиления входных сигналов с минимальными линейными искажениями рабочую точку n выбирают на середине линейного участка переходной характеристики Iк=f(IБ) (рис. 2.2). Этому режиму должны соответствовать определенные значения токов IБn, Iкn и напряжений VБn, Vкn. На практике для транзисторов малой и средней мощности токи транзистора и напряжения на нем в режиме покоя выбирают приблизительно такими:

VкnEк/2, Iкn(Eк/2)/Rк, IБn Iкn/h21. (2.1)

При этом VБn0,3 В для германиевых и VБn0,65 В для кремниевых транзисторов.

Указанный режим обеспечивается сопротивлением резистора RБ, определяемым по формуле

RБ=(Ек–VБn)/IБn Ек/IБn. (2.2)

Конденсатор Сс1 включают на входе усилителя для того, чтобы не создавать постоянной составляющей тока в источнике усиливаемых сигналов Vвх за счет действия источника питания Ек. Кроме того, при отсутствии Сс1 нарушается режим работы усилителя по постоянной составляющей.

При подаче на вход усилителя переменного входного напряжения Vвх напряжение VБэ становится пульсирующим (рис. 2.2) VБэ= VБn+ Vвх. Это вызывает пульсации базового тока IБ= IБn+ IБ, коллекторного тока Iк= Iкn+ Iк и коллекторного напряжения Vк=Vкn+ Vк.

Конденсатор Сс2 (конденсатор связи) задерживает постоянную составляющую коллекторного напряжения и пропускает в нагрузочное устройство усилителя только переменную составляющую Vк, являющуюся выходным напряжением усилителя.

Если изменение входного напряжения Vвх базового IБ и Iк токов укладываются в линейные участки входной и передаточной характеристик, то форма выходного напряжения будет соответствовать форме входного напряжения (рис.2.2). При больших входных сигналах, при которых базовые и коллекторные токи выходят за пределы линейного участка ab передаточной характеристики, форма выходного напряжения значительно искажается. Эти искажения обусловлены нелинейностью вольт-амперных характеристик.

Для оценки диапазона изменений входных напряжений, усиливаемых без искажений, используют амплитудную характеристику Vвых m=f(Vвх m), представляющую собой зависимость амплитудного значения выходного напряжения от амплитудного значения входного напряжения (рис. 2.3).

По амплитудной характеристике в линейной ее части (участок 0n) можно определить коэффициент усиления КV. На участке nк коэффициент усиления уменьшается, что объясняется выходом усиливаемого сигнала за пределы линейного участка ab передаточной характеристики (см. рис. 2.2). Амплитудная характеристика позволяет выявить динамический диапазон усилителя, который определяется напряжением Vвых m, ограничиваемым допустимыми нелинейными искажениями.

При работе усилителя в линейном режиме, т.е. без нелинейных искажений, все основные параметры усилителя на биполярном транзисторе (KV, Rвх, Rвых) можно рассчитать с помощью схемы замещения усилителя для переменных составляющих токов и напряжений (рис. 2.4.). Построенные схемы замещения усилителя начинают со схемы замещения транзистора, включенного по схеме с общим эмиттером (обведена пунктиром). При этом следует учесть, что по переменной составляющей тока узел А (см. рис. 2.1, а) соединен с общей точкой усилителя, так как внутреннее сопротивление источника Ек по переменной составляющей мало.

В схеме замещения отсутствуют оба конденсатора, поскольку их сопротивления по переменной составляющей весьма малы и ими пренебрегают. На схеме замещения не представлен также резистор RБ, так как его сопротивление много больше h11.

Для определения коэффициента усиления усилителя с ОЭ запишем для узла к схемы замещения уравнение по первому закону Кирхгофа (при Rн=)

![]() (2.3)

(2.3)

Входное напряжение определяется по формуле

![]() (2.4)

(2.4)

Решая совместно уравнения (2.3) и (2.4), получим (при Rн=)

![]() (2.5)

(2.5)

Так как h22Rк обычно много меньше единицы, то

![]() (2.6)

(2.6)

Знак «–» выражении (2.5) означает, что входное и выходное напряжение находится в противофазе.

Из схемы замещения рис. 2.4 легко получить выражения для входного и выходного сопротивления усилителя

Rвх=h11, (2.7)

![]() (2.8)

(2.8)

Входное сопротивление усилительного каскада с общим эмиттером обычно определяют по справочнику, где указаны значения h-параметров. Для транзисторов малой и средней мощности оно, как правило, лежит в пределах от нескольких десятков Ом до единиц кОм. Выходное сопротивление усилителя с ОЭ обычно больше входного, поскольку оно определяется сопротивлением Rк, имеющим, как правило, значения несколько кОм. Это создает значительные трудности и в работе усилителя с высокоомным источником усиливаемого напряжения и низкоомным загрузочным устройством. Коэффициент усиления усилителя с учетом внутреннего сопротивления источника переменного напряжения и сопротивления нагрузочного устройства определяют по формуле

![]() (2.9)

(2.9)

Существенным недостатком транзисторов является зависимость их параметров от температуры, что приводит к изменению коллекторных характеристик транзистора (пунктирные кривые на рис. 2.5). Вследствие этого при изменениях температуры изменяется положение рабочей точки усилителя (например точка n’ на рис. 2.5), что может вызвать искажение выходного напряжения. Для предотвращения этого требуется температурная стабилизация рабочей точки. На рис. 2.6 изображена схема усилителя с ОЭ с эмиттерной температурной стабилизацией, которая фиксирует рабочую точку за счет отрицательной обратной связи по постоянному току, возникающей благодаря включению в эмиттерную цепь усилителя резистора Rэ. Резисторы RБ’ и RБ’’ необходимы для создания требуемого напряжения VБэn в режиме покоя

(2.10)

(2.10)

При повышении температуры увеличивается ток Iэn Iкn, а следовательно, падение напряжения на резисторе Rэ, поэтому напряжение VБэn уменьшается. Это вызывает уменьшение базового тока IБn, что приводит к уменьшению тока Iкn почти до первоначального значения. Для устранения отрицательной обратной связи по переменной составляющей, которая появляется при наличии напряжения Vвх, резистор Rэ шунтируют конденсатором Сэ, сопротивление 1/Сэ которого на низшей частоте усиливаемого сигнала должно быть на порядок меньше Rэ. При таком выборе емкости Сэ отрицательная обратная связь по переменной составляющей практически будет отсутствовать.

В усилителе с ОЭ с эмиттерной стабилизацией рекомендуется режим

Vкn(2/3)Eк; Vэn(1/3)Eк. (2.11)

Усилитель (рис. 2.7, а), в котором транзистор включен по схеме с общим коллектором, называют эмиттерным повторителем. В этом усилителе основной резистор, с которого снимается выходное напряжение, включен в эмиттерную цепь. Коллектор транзистора по переменной составляющей напряжения соединен с общей точкой.

Для определения основных параметров эмиттерного повторителя следует рассмотреть его упрощенную схему замещения, изображенную на рис. 2.7, б (при условии 1/h22Rэ). В этой схеме h11 и h21 являются параметрами транзистора при включении его по схеме с ОЭ, сопротивление резисторного элемента Rэн= RэRн/(Rэ+ Rн).

Резисторы RБ’ и RБ’’ в этой схеме не представлены по той причине, что и резистор RБ в схеме замещения усилителя с ОЭ. Нетрудно убедиться, что

![]() (2.12)

(2.12)

![]() (2.13)

(2.13)

![]() (2.14)

(2.14)

В этом усилителе обычно KV0,9—0,99, Rвх примерно в (1+h21) раз больше, а Rвых — в (1+h21) раз меньше, чем в усилителе с общим эмиттером. Обычно для транзисторов малой и средней мощностей Rвх равно нескольким к Ом, а Rвых колеблется от нескольких до десятков Ом. В режиме покоя эмиттерного повторителя рекомендуется, чтобы Vэп0,5Ек.

Таким образом, эмиттерный повторитель имеет большое входное и малое выходное сопротивления. Поэтому его применяют для согласования высокоомного источника усиливаемого сигнала с низкоомным нагрузочным устройством.

В последние годы в усилителях на дискретных элементах и в интегральных микросхемах стали применять составные транзисторы, представляющие собой комбинацию из двух каскадно включенных транзисторов. Чаще других используют комбинацию, известную под названием схемы Дарлингтона (рис. 2.8).

Как видно из схемы, составной транзистор имеет три вывода, эквивалентные эмиттеру, базе и коллектору. Поэтому его можно рассматривать как единый транзистор, обладающий определенными параметрами. Основными параметрами составного транзистора являются коэффициент усиления по току h21 и резистивный параметр h11

h21=h21,1h21,2 (2.15)

h11=h11,1+(1+h21,1)h11,2 (2.16)

В настоящее время составные транзисторы выпускаются в виде отдельных приборов. Например широко используется составной транзистор КТ827, параметры которого представлены в справочнике.

Составные транзисторы находят применение в усилителях с ОЭ. Особенно часто составной (по схеме Дарлингтона) транзистор применяется в эмиттерных повторителях. Анализ изменений основных параметров эмиттерного повторителя на составном транзисторе по формулам (2.15) и (2.16) показывает, что он имеет более высокое входное и более низкое выходное сопротивление.

Усилители на полевых транзисторах

В последние годы начали широко применять усилители на полевых транзисторах, так как они обладают существенно большим входным сопротивлением, температурной стабильностью и радиационной стойкостью по сравнению с усилителями на биполярных транзисторах. Однако их частотные свойства хуже, чем у аналогичных усилителей на биполярных транзисторах.

Построение усилителей на полевых транзисторах осуществляется также, как и на биполярных транзисторах.

Различают усилители с общим истоком (ОИ) и с общим стоком (ОС).

Наибольшее распространение получили усилители с общим истоком, простейшая схема которого выполнена на МОП-транзисторе рис. 2.9.

В этом усилителе резистор RC, с помощью которого создается выходное напряжение, включен в цепь стока. Так же, как и в усилителе с ОЭ, входное напряжение Vвх от источника сигналов евх подается на усилительный каскад через конденсатор связи СС1, а выходное (усиленное) напряжение снимается с транзистора и подается на нагрузочный резистор Rн через конденсатор связи СС2. Резистор RЗ в цепи затвора обеспечивает подачу на затвор отрицательного по отношению к истоку потенциала, создаваемого за счет падения напряжения на резисторе. Сопротивление резистора RЗ для полевого транзистора должно быть не более 0,1—0,03 от номинального сопротивления постоянному току промежутка затвор-исток. Для МОП-транзистора это сопротивление берут обычно равным 1 МОм.

Такой выбор сопротивления RЗ практически исключает влияние разброса сопротивления промежутка затвор-исток транзистора на входное сопротивление усилителя.

Принцип выбора режима покоя в рассматриваемом усилителе такой же, как и в усилителе на биполярном транзисторе. Это видно из рис. 2.10, где приведен графический анализ работы усилителя с общим истоком. Напряжение смещения VЗn должно быть больше или равно Vвх max. В этом режиме в транзисторе появляется ток IСn, а между стоком и истоком возникает напряжение VCn.

При возникновении напряжения Vвх ток стока IС начинает пульсировать, вызывая появление переменной составляющей стокового напряжения, являющейся усиленным выходным напряжением усилителя.

Выбрав рабочую точку n на середине сток-затворной динамической характеристики IС=f(VЗ) (рис. 2.10), определяем напряжение VЗn. Тогда Rн=VЗn/ IСn .

Емкость конденсатора Си, предназначенного для устранения отрицательной обратной связи при Vвх0, выбирают из соотношения

Си=(1020)/)нRи, (2.17)

где н — нижняя угловая частота усиливаемого напряжения.

Звено автоматического смещения RиСи является также звеном температурной стабилизации, как и в усилителе на биполярном транзисторе.

Для определения основных параметров усилительного каскада на полевом транзисторе используют схему замещения усилителя, изображенную на рис. 2.11.

Коэффициент усиления усилителя

![]() (2.18)

(2.18)

где S — крутизна, а Ri — внутреннее сопротивление полевого транзистора.

Входное сопротивление усилительного каскада на полевом транзисторе

Rвх=RЗ. (2.19)

Усилители на МОП-транзисторах имеют входное сопротивление, равное нескольким МОм.

Сопротивление стокового резистора RC выбирают из соотношения RC103104 Ом. Как видно из схемы замещения, выходное сопротивление

Rвых=RiRC/(Ri+RC)RC, (2.20)

так как RC Ri.

Обычно сопротивление Rвых составляет несколько кОм. Таким образом, в усилителе с ОИ на полевом транзисторе в отличие от усилителя на биполярном транзисторе выходное сопротивление много меньше входного

Помимо усилителя с ОИ часто применяют усилитель с общим стоком (ОС), называемый также истоковым повторителем (2.12).

В этом усилителе нагрузочный резистор Rн включен в цепь истока, а сток по переменной составляющей тока и напряжения соединен с общей шиной усилителя. Выходное напряжение, равное переменной составляющей падения напряжения на резисторе, снимается через конденсатор связи СС2.

Амплитудно-частотная характеристика усилителя

При усилении входных сигналов, частота которых изменяется от нижней частоты н до некоторой высокой частоты в на коэффициент усиления КV=КVej (как на его модуль КV,так и на аргумент ) начинают влиять частотные свойства транзисторов, емкостные сопротивления конденсаторов связи СС и паразитные емкости в усилителе. Анализ этого влияния приведен на примере усилителя на биполярном транзисторе. Для этого воспользуемся схемой замещения усилителя, изображенной на рис. 2.13. В этой схеме помимо известных элементов в схеме замещения рис. 2.4 имеются новые элементы: конденсатор связи СС и емкостный элемент С0=(1КV)Ск+См, где КV — это коэффициент усиления по напряжению усилителя, Ск — емкость коллекторного перехода транзистора, См — емкость монтажа.

Емкость С0 может иметь значение от нескольких десятков до нескольких сотен пикофарад.

Важной характеристикой усилителя, работающего в широком диапазоне частот, является амплитудно-частотная характеристика, представляющая собой зависимость модуля коэффициента усиления усилителя КV от частоты.

При работе усилителя на средних частотах, являющимися рабочими частотами, коэффициент усиления К0 имеет почти постоянное (максимальное) значение. В этой области частот влиянием СС и С0 можно пренебречь, так как емкостное сопротивление XСс очень велико по сравнению с Rвых усилителя, а ХСв очень велико по сравнению с Rн. Тогда коэффициент усиления будет действительным числом

![]() (2.21)

(2.21)

Так как h22Rк1, то

![]() (2.21,

а)

(2.21,

а)

Обычно рассматривают нормированную амплитудно-частотную характеристику К/К0=(f) (рис. 2.14). На нижних частотах влиянием емкостного элемента пренебрегают, поскольку его сопротивление XC становится еще больше, чем в рабочем диапазоне частот. В то же время на нижних частотах сопротивление ХСс=1/(нСС) также становится большим (емкость СС равна десятым долям и единицам микрофарад). Падение напряжения на конденсаторе связи СС с уменьшением частот возрастает, выходное напряжение уменьшается и, следовательно, коэффициент усиления также уменьшается.

На нижних частотах коэффициент усиления определяется по формуле

![]() (2.22)

(2.22)

где н=СС(Rвых+Rн). Так как Rвых Rк, то н=СС(Rк+Rн).

При работе на верхних частотах влиянием конденсатора связи пренебрегают, так как его сопротивление становится весьма малым. При этом, однако, следует учитывать влияние емкостного элемента С0, так как его сопротивление становится тоже малым и начинает шунтировать, нагрузочный резистор Rн. В результате выходное напряжение и коэффициент уменьшаются. В этом случае коэффициент усиления

![]() (2.23)

(2.23)

где

![]()

Уменьшение коэффициента усиления оценивают коэффициентами частотных искажений Мн=К0/Кн и Мв=К0/Кв.

Частоты fн, fв, на которых коэффициенты усиления Кн, Кв достигают допустимых значений, называют границей полосы пропускания усилителя в области нижних (fн) и верхних (fв) частот. Обычно принимают К0/Кн= К0/Кв=21,41.

При каскадном соединении усилителей общий коэффициент усиления возрастает, но увеличиваются и коэффициенты частотных искажений, т.е. полоса пропускания многокаскадного усилителя всегда уже полосы пропускания каждого из простейших усилителей. Для усилителей с конденсаторной связью полоса пропускания обычно от 20—200 Гц до 150—500 кГц.

Операционные усилители

Операционными усилителями (ОУ) называют усилитель электрических сигналов, предназначенный для выполнения различных операций над аналоговыми и импульсными величинами при работе с обратными связями.

В настоящее время промышленность выпускает операционные усилители второго и третьего поколений, построенные по двухкаскадной схеме. Эти ОУ по своим основным параметрам значительно превосходят операционные усилители первого поколения, создаваемые по трехкаскадной схеме.

Основу всех ОУ составляют дифференциальные каскады.

Первый каскад обеспечивает коэффициент усиления, достигающий нескольких сотен тысяч и единиц миллионов. Входной каскад, в котором часто используются полевые транзисторы, обеспечивает входные характеристики ОУ, в частности его высокое входное сопротивление. Выходным каскадом является бестрансформаторный двухтактный усилитель мощности (эмиттерный повторитель, работающий в режиме усиления В или АВ). Он служит для согласования высокого выходного сопротивления первого дифференциального каскада ОУ с низкоомным нагрузочным устройством. Поэтому ОУ имеет низкое выходное сопротивление. Кроме того, в состав современных ОУ входят цепи защиты по входу от перенапряжения и по выходу от превышения выходного тока.

В настоящее время операционные усилители, изготавливаемые по интегральной технологии, являются самыми универсальными и массовыми аналоговыми устройствами. ОУ широко применяются не только в усилителях, но также в различных генераторах, преобразователях, стабилизаторах напряжения, компараторах, источниках эталонных напряжений, активных фильтрах, электронных ключах и т.д.

Широкие функциональные возможности при небольшом числе стандартных типов ОУ, выпускаемых промышленностью, достигаются за счет включения разнообразных внешних цепей обратных связей. Наибольшее распространение получили интегральные полупроводниковые ОУ, обладающие наименьшими габаритами и массой, и способные работать в диапазоне температур –60 до +125 С. Они имеют коэффициент усиления 106 и более при усилении сигналов частотой от нуля до единицы сотен МГц. На работу подобных ОУ весьма слабо влияют такие дестабилизирующие факторы, как изменение температуры и питающего напряжения.

Современные ОУ относительно дешевы и доступны для широкого применения, что обеспечивается их массовым автоматизированным изготовлением. Надежность операционного усилителя, включающего в себя несколько сотен элементов и более, соответствует надежности отдельного транзистора, что обеспечивается интегральной технологией, при которой все элементы (транзисторы, диоды, резисторы и др.) и соединения между ними выполняются в едином технологическом цикле. Как показывает практика, срок службы хорошего полупроводникового ОУ может превысить 20 лет /2/.

На рис 2.15, а приведено условное обозначение операционного усилителя. Как видно, ОУ имеет два входа и один выход. Вход, напряжение на котором сдвинуто по фазе на 180 относительно выходного напряжения, называют инвертирующим и обозначают кружком. Второй вход является неинвентирующим, так как напряжение на нем и выходное напряжение совпадает по фазе.

Выводы, к которым подключаются источники питающего напряжения +Vип и Vип, а также вспомогательные цепи на принципиальных схемах обычно не обозначают. При необходимости выводы ОУ, к которым подключаются источники напряжения, изображают так, как показано на рис. 2.15, б.

На рис. 2.16 изображена одна из важнейших характеристик — амплитудная (передаточная) характеристика ОУ, представляющая собой зависимость Vвых=f(Vвх) при нулевой частоте. Кривая 1 соответствует подаче входного напряжения на инвертирующий вход, кривая 2 — на неинвентирующий вход. Эти характеристики получают при подаче входного напряжения на один из входов при отсутствии напряжения на другом входе. Наклонный (линейный) участок кривых подчеркивает нелинейность зависимости Vвых=f(Vвх). Горизонтальные участки кривых соответствуют режиму работы ОУ, при котором входное напряжение выходит за пределы линейного участка передаточной характеристики.

Значения выходного напряжения и V +вых max и V –вых max характеризующие эти участки, обычно на 1—2 В меньше напряжения питания.

Операционный усилитель характеризуется теми же параметрами, что и другие усилители. Значения параметров интегральных ОУ позволяют быстро и грамотно спроектировать различные электронные блоки и устройства, а также предотвратить выход их из строя, т.е. работу в недопустимых режимах.

Современные ОУ имеют следующие основные параметры:

Коэффициент усиления КV. Представляет собой отношение приращения выходного напряжения к вызвавшему его приращению входного напряжения. В современных ОУ КV при нулевой частоте достигает значений от десятков и сотен тысяч до нескольких миллионов. По углу наклона линейного участка амплитудной характеристики определяют коэффициент усиления.

Коэффициент усиления ОУ зависит от изменения напряжения питания, тока нагрузочного устройства, температуры окружающей среды. По этой причине ОУ (за исключением компараторов) не применяют без цепей внешней обратной связи, которые стабилизируют коэффициент усиления.

Напряжение смещения Vсм. Определяется входным напряжением, при котором выходное напряжение равно нулю (рис. 3.2). Напряжение смещения появляется вследствие разброса параметров элементов ОУ или изменений режимов работы входных транзисторов за счет рассогласования во входных цепях ОУ. Обычно в ОУ широкого применения Vсм=5—20 мВ. Напряжение смещения зависит от температуры и напряжения источника питания. Изменение Vсм в зависимости от температуры для ОУ широкого применения составляет примерно 50 мкВ/К. Для устранения напряжения смещения на входе ОУ вводят специальные электрические цепи.

Входной ток Iвх. Это ток во входной цепи ОУ, который может составить 100 мкА. Его необходимо учитывать при подключении к обоим входам внешних электрических цепей. Если сопротивление внешних электрических цепей по инвертирующему и неинвентирующему входам неодинаковые, то разность падений напряжений на них вызовет дополнительные напряжения, складывающиеся с напряжением смещения. Для исключения этого сопротивления этих выводов стремятся сделать равными.

Входное сопротивление Rвх. Различают входное сопротивление для дифференциального сигнала (Rвх д) и синфазного сигнала (Rвх сф). Для получения большого входного сопротивления первый каскад ОУ выполняют на полевых транзисторах; Rвх д имеет значение от нескольких кОм для биполярных транзисторов до нескольких единиц и десятков МОм для полевых транзисторов, а Rвх сф 100 МОм.

Выходное сопротивление Rвых. Это сопротивление, измеренное со стороны загрузочного устройства, представляет собой выходное сопротивление выходных каскадов ОУ, построенных на эмиттерных повторителях. Значения Rвых=20—2000 Ом.

Усиление сигналов различных частот определяется амплитудно-частотной характеристикой ОУ (рис. 2.17, а), а усиление импульсных (обычно прямоугольных) сигналов скоростью нарастания выходного напряжения (рис. 2.17, б).

В соответствии с этим вводят динамические параметры ОУ:

частоту среза fср, значение которой соответствует снижению модуля коэффициента ОУ в 2 раза (3дБ);

частоту единичного усиления fт, при которой модуль коэффициента усиления ОУ уменьшается до единицы (для современных ОУ fт=15—20 МГц);

максимальную скорость нарастания выходного напряжения VV вых, определяющую наибольшую скорость изменения выходного напряжения ОУ (рис. 3.3, б) при воздействии прямоугольного входного импульса; скорость нарастания определяется как отношение Vвых к t (для современных ОУ VV вых=0,1—100 В/мкс);

время установления tуст, определяющее изменение выходного напряжения ОУ от уровня 0,1 (рис. 3.3, б) до уровня 0,9 от установившегося выходного напряжения при воздействии на вход прямоугольного импульса (для ОУ широкого применения tуст=0,05—2 мкс).

Одним из важных достоинств ОУ является подавление синфазных сигналов. Поэтому ОУ характеризуется коэффициентом ослабления синфазных сигналов КОСС=20lg(КССР/КV) (для ОУ общего назначения КОС ССР=70—120 дБ).

Выпускаемые в настоящее время интегральные ОУ квалифицируют по следующим группам:

ОУ общего назначения, составляющие наиболее многочисленную группу универсальных ОУ;

прецизионные ОУ, позволяющие поддерживать с высокой точностью большой коэффициент усиления КV: они имеют высокое входное сопротивление и малое напряжение смещения (Vсм0,5 мВ), типичным прецизионным ОУ является интегральная микросхема 133УД5;

быстродействующие ОУ, характеризующиеся повышенной скоростью нарастания выходного напряжения и малым временем установления. Они имеют частоту единичного усиления 15—20 МГц (например, ОУ 140УД10 и КР544УД2);

микромощные ОУ, потребляющие наименьшую энергию от источника питания (например, ОУ 140УД12, Iпотр 0,18 мА при Vип=6 В).

Наиболее широко используется ИМС серии 140 и 153.

Операционные усилители рассчитаны на применение симметричных равнополярных источников питания напряжением от 5 до 27 В. В настоящее время чаще всего используют напряжения 5 и 15 В с допускаемым отклонением (5—10) %.

Применение подобных источников питания упрощает задачу компенсации смещения нуля ОУ и предотвращает появление ненужной постоянной составляющей тока в нагрузочном устройстве.

Для анализа работы ОУ часто пользуются схемой замещения, изображенной на рис. 3.4. Входная часть схемы замещения определяется входным дифференциальным сопротивлением Rвх д, а выходная часть содержит источник ЭДС К0(f)Vвх и резистивный элемент с сопротивлением Rвых.

Для удобства расчетов устройств с ОУ вводят понятие идеального ОУ, у которого:

коэффициент усиления стремится к бесконечности;

входное дифференциальное сопротивление Rвх д стремиться к бесконечности;

выходное сопротивление Rвых стремится к нулю;

выходное напряжение равно нулю при нулевом входном напряжении.

Применение операционных усилителей. При использовании ОУ в качестве инвертирующего усилителя (рис. 2.19, а) выходное напряжение сдвинуто по отношению к входному на 180. Входное напряжение Vвх подается на инвертирующий вход через резистор R1. С помощью резистора RОС осуществляется отрицательная параллельная обратная связь по напряжению. Неинвертирующий вход усилителя при этом заземлен. В соответствии с первым законом Кирхгофа для узла а уравнение токов записывается в виде

![]() (2.24)

(2.24)

Анализ рассматриваемой схемы включения ОУ значительно упрощается при допущении, что ОУ идеален. Тогда при любом значении Rн0 и конечном значении выходного напряжения входное напряжение будет равно нулю. В этом случае инвертирующий и неинвертирующий входы при Vвх=0 как бы замкнуты накоротко. Это так называемое виртуальное замыкание. В отличие от обычного короткого замыкания при виртуальном замыкании ток между входами ОУ отсутствует, т.е. Iоу=0 и Iвх= Iос. Тогда Vвх= R1Iвх и Vвых=–RосIос.

Коэффициент усиления инвертирующего усиления

![]() (2.25)

(2.25)

Знак «–» в выражении (2.25) означает, что в инвертирующем усилителе входное и выходное напряжение находятся в противофазе. Нетрудно убедиться, что входное сопротивление инвертирующего усилителя

Rвх ос=R1. (2.26)

Выходное сопротивление

![]() (2.26,

а)

(2.26,

а)

При КV значение Rвых ос будет стремиться к нулю. Для устранения различия сопротивлений во входных цепях по инвертирующему и неинвертирующему входам ОУ, вызванного подключением к инвертирующему входу резистора R1, Rос в цепь неинвертирующего входа включают резистор R2=R1Rос(R1+Rос) (рис. 3.5, б).

Если входной сигнал подать на инвертирующий вход ОУ, а на инвертирующий вход с помощью цепи обратной связи R1, Rос подать часть выходного напряжения, т.е. осуществить последовательную отрицательную обратную связь по напряжению, то получится неинвертирующий усилитель (рис. 3.6, а). При таком виде обратной связи в соответствии со вторым законом Кирхгофа для входной цепи уравнение запишется так

![]() .

(2.27)

.

(2.27)

Вследствие виртуального замыкания инвертирующего и неинвертирующего входов V0=0, тогда

![]() (2.28)

(2.28)

Коэффициент усиления неинвертирующего усилителя

![]() (2.29)

(2.29)

Входное сопротивление этого усилителя

![]() (2.30)

(2.30)

где

![]() — коэффициент обратной связи.

— коэффициент обратной связи.

При КV входное сопротивление стремится к бесконечности.

Из формулы (2.30) видно, что входное сопротивление неинвертирующего усилителя довольно большое. Отметим, что значение Rвх ос у неинвертирующего усилителя значительно больше, чем у инвертирующего.

Выходное сопротивление неинвертирующего усилителя

![]() (2.31)

(2.31)

При КV выходное сопротивление стремится к нулю.

Учитывая, что у неинвертирующего усилителя сопротивление Rвх ос очень большое, Rвых ос мало, такой усилитель применяют часто, как согласующий элемент при работе с высокоомным источником сигнала и низкоомным нагрузочным устройством.

Обычно для усилителей большое входное сопротивление не нужно, так как при этом они оказались бы весьма чувствительными к изменению входного тока флуктуационного происхождения. Поэтому во входную цепь усилителя включают резистор R2Rвх1 д, который должен определять входное сопротивление неинвертирующего усилителя. Значение сопротивления R2 выбирают в пределах 0,5—1 МОм.

На рис. 2.20, б изображена схема низкочастотного неинвертирующего усилителя, в котором введена раздельная обратная связь по переменной и постоянной составляющим. Для полезного (усиливаемого) сигнала коэффициент обратной связи =R1/(R1+ Rос), так как емкость конденсатора С2 выбирают такой, чтобы можно было пренебречь его сопротивлением в частотном диапазоне усиливаемых напряжений (XC2R1 на самой нижней частоте частотного диапазона). Для постоянной составляющей, определяемой напряжением Vсм, благодаря тому, что XC2= действует 100%-ная отрицательная обратная связь (КVос=1). Если не предусмотреть подавления напряжения смещения Vсм, то транзисторы ОУ могут войти в режим насыщения, что вызовет нелинейные искажения в работе усилителя и снижение коэффициента усиления.

Устранение Vсм в усилителях на ОУ производится чаще подключением потенциометра RБЛЛ к специальным выводам ОУ. Как отмечалось, на основе двух ОУ — инвертирующего и неинвертирующего — при использовании различных цепей обратных связей строят разнообразные электронные устройства. На основе инвертирующего усилителя можно построить сумматор (рис. 2.21).

Если по-прежнему считать ОУ идеальным, то при подаче на инвертирующий вход ОУ через резисторы R1, R2, ...Rn входных напряжений V1, V2,... Vn выходное напряжение в соответствии с выражением (2.25) будет равно сумме входных напряжений

Rвых=–Rос/R0(V1+ V2+... +Vn), (2.32)

где R0= R1’= R1’’=...= Rn, R0 Rвх д.

Если в инвертирующем усилителе (см. рис. 3.5) резистор заменить конденсатором Сос, то получится интегратор (рис. 3.8, а). Действительно, Vвх=R1iвх, а Vвых=VC. Так как iвх=– iос=–СосdVвых/dt, то Vвх/R1=–CосdVвых/dt. Следовательно,

![]() (2.33)

(2.33)

При замене резистора R1 конденсатором С1 схема (рис. 3.5) превращается в схему дифференциатора (рис. 3.9, а). Так как Vвх= VС, а Vвых=– Rос iос, то учитывая, что iос=С1dVвх/dt получим

![]() (2.34)

(2.34)

Как известно из электротехники, в интегрирующих и дифференцирующих RC-цепях степень точности дифференцирования и интегрирования входного сигнала зависит от степени выполнения неравенства lвыхVвх. Чем точнее RC- цепь производит ту или иную названную операцию, тем меньше должно быть выходное напряжение. Нетрудно убедиться, что интегратор на ОУ эквивалентен интегрирующей RC’-цепи (рис. 3.8, б), где С’=CКV напряжение с выхода которой усиливается ОУ в КV раз.

Т акже

можно проанализировать работу

дифференциатора на ОУ, схема которого

эквивалентна дифференцирующей RC’-цепи

(рис. 2.23, б), где R’=R/KV

напряжение с выхода которой усиливается

ОУ в KV

раз.

акже

можно проанализировать работу

дифференциатора на ОУ, схема которого

эквивалентна дифференцирующей RC’-цепи

(рис. 2.23, б), где R’=R/KV

напряжение с выхода которой усиливается

ОУ в KV

раз.

Интеграторы и дифференциаторы на ОУ в настоящее время полностью вытеснили соответствующие RС-цепи из импульсной и вычислительной техники из-за более высокой точности. Если ввести интегродиффиренцирующую обратную связь в ОУ, как показано на рис. 3.10, то получится избирательный RC-усилитель. Такой усилитель на частоте квазирезонанса f0=1/(2R1R2C1C2) имеет максимальный коэффициент усиления, определяемый по формуле

![]() (2.35)

(2.35)

2.1.2. Стабилизаторы напряжения

Параметрические стабилизаторы напряжения.

В тех случаях, когда необходимо исключить изменения выходного постоянного напряжения, используют различные методы стабилизации. Стабилизация уменьшает как изменения Uнср, так и пульсации до весьма малых значений.

В схемах полупроводниковых стабилизаторов широко используются стабилитроны. Стабилитрон - это кремниевый диод c определенной технологией изготовления р-n -перехода. При приложении обратного напряжения наступает обратимый электрический пробой и ВАХ имеет участок стабильного напряжения (рис.2.25). Параметрами стабилитрона являются: напряжение стабилизации (от единиц вольт до 180 В), минимальный и максимальный ток стабилизации; допустимая мощность, выделяемая на стабилитроне в режиме стабилизации. Наклон ветви стабилизации ВАХ по отношению к оси тока определяется дифференциальным сопротивлением весьма малого значения. В области прямых напряжений стабилитрон имеет ВАХ обычного маломощного кремниевого диода.

Рис.2.25 Рис. 2.26

Одним из типов стабилизаторов является параметрический стабилизатор напряжения.(рис.2.26). В схеме V1–стабилитрон, рабочий режим которого выбран на ветви стабилизации его ВАХ. Сопротивление нагрузки Rн подключается к выходным клеммам стабилизатора, т.е. параллельно стабилитрону. Напряжение Uн является напряжением на стабилитроне. Из-за малого значения дифференциального сопротивления оно мало меняется при изменении входного напряжения. Разность входного напряжения и стабилизированного напряжения на нагрузке Uн падает на резисторе R1 .

Количественно стабилизирующие свойства выясняются применением графоаналитического метода расчета цепей с нелинейными элементами. Анализируемая cxeмa разделяется на линейную часть и нелинейный элемент (рис. 2.26).

Рис. 2.27

Изменения Rн не повлияют на положение точки 2. Координаты же точки 1 будут различными. В режиме холостого хода стабилизатора. В режиме номинальной нагрузки стабилизатора, например, при Rн=R1 координата Uab=0,5 Uвх (точка 1'). Кок видно из графического построения, принятый диапазон изменения вызовет незначительное изменение напряжения на стабилитроне.

Стабилизация напряжения на нагрузке при нестабильности входного напряжения характеризуется коэффициентом стабилизации:

![]()

При этом ΔUвх может быть обусловлено как случайным изменением входного напряжения, так и пульсациями. Используя параметрический стабилизатор, трудно получить коэффициент стабилизации более 5-6. Лучшими стабилизирующими свойствами обладают стабилизаторы с более сложными схемами. Полупроводниковые стабилизаторы, как правило, применяются для получения стабильного напряжения питания электронных и измерительных устройств сравнительно небольшой мощности до десятков ватт.

Компенсационные стабилизаторы напряжения

В отличие от параметрических, компенсационные стабилизаторы напряжения обеспечивают необходимую стабильность напряжения на нагрузке при помощи отрицательной обратной связи, воздействующей на регулирующий элемент (РЭ). В зависимости от схемы включения РЭ компенсационные стабилизаторы разделяются на последовательные и параллельные. На рис.2.28 приведена схема одного из наиболее распространенных (до появления интегральных стабилизаторов) транзисторных стабилизаторов напряжения последовательного типа. Стабилизатор состоит из регулирующего элемента (транзисторы VT1, VT2, VT3), усилителя постоянного тока (VT0, R1), опорного напряжения (VD,R2), делителя напряжения R3-R5, резисторов R6, R7, используемых для выбора режима по постоянному току транзисторов VT1, VT2, и конденсатора С. В стабилизаторе предусмотрена регулировка выходного напряжения, для чего в состав делителя включен потенциометр R4.

Рис.2.28. Компенсационный стабилизатор

Число транзисторов, входящих в регулируемый элемент, зависит от типа нагрузки. При In<(0,02…0,03) А можно использовать только один транзистор VT1; при (0,02…0,03)А<In<(0,5…0,6)А - два транзистора VT1, VT2; при (0,5…0,6)А<In<(4…5)А - все три транзистора. Стабилизатор может быть выполнен на транзисторах типа p-n-p или n-p-n. При использовании транзисторов типа p-n-p полярности напряжений на входе и выходе изменяются на противоположные (по сравнению со схемой на рис.2.28). При этом необходимо также переключить стабилитрон VD, чтобы напряжение на его аноде было положительным относительно катода. Стабилизатор работает следующим образом. При увеличении входного напряжения Ui увеличивается и выходное напряжение U0, что вызывает увеличение напряжения на входе транзистора VT0 и его коллекторного тока, в результате чего напряжение на коллекторе уменьшается, а это вызывает уменьшение тока через транзисторы РЭ и, следовательно, приводит к пропорциональному уменьшению U0. Аналогичные процессы происходят и при уменьшении тока нагрузки, что приводит к увеличению U0. При уменьшении Ui или U0 (при увеличении тока нагрузки) транзистор VT0 подзакрывается, напряжение на его коллекторе и на базе транзистора РЭ увеличивается, в результате чего U0 увеличивается почти до номинального значения. Для проведения моделирования необходимо предварительно провести приближенный расчет. Исходные данные для такого расчета:

номинальное выходное напряжение U0, В;

пределы регулирования выходного напряжения U0max-U0min,В;

ток нагрузки IHmax,А;

минимальное и максимальное напряжения сети Uimin, Uimax,В. Примерный порядок предварительного расчета:

Определяем минимальное входное напряжение Uimin=U0max+(4...5) В. Добавить 4-5 В требуется для обеспечения нормальной работы транзисторов РЭ. Максимальное Uimax в этом случае задается из условия максимально возможного напряжения сети.

В зависимости от тока нагрузки определяем число транзисторов, входящих в схему (см. вышеперечисленную рекомендацию).

По Uimax-U0max и IHmax выбираются типы транзисторов по максимально допустимым напряжению и току коллектора.

Выбирается тип стабилитрона VD по напряжению стабилизации из условия Us=U0min-(2–3) вольта. В этом случае сопротивление резистора R2=(2–3)/ISmin , где ISmin - минимальный ток стабилизации стабилитрона. Так, например, при ISmin=5 мА R2=400…600 Ом.

Определяется сопротивление резистора R1 из условия, что при напряжении Uimin-U0max по нему протекает ток 3…5 мА.

Определяется суммарное Rs сопротивление резисторов делителя R3-R5 из условия протекания по нему тока 5-10 мА при номинальном напряжении U0. При этом сопротивления резисторов делителя определяются из выражения R5=RsUs/U0max, R4=Rs/U0min, R3=Rs-R4-R5.

Сопротивления резисторов R7, R6 определяются как U0/Ibeo, где Ibeo- тепловой ток эмиттерного перехода соответствующего транзистора.

Рассмотренный стабилизатор обладает сравнительно небольшим коэффициентом стабилизации из-за малого коэффициента усиления однокаскадного усилителя постоянного тока (УПТ). Более высокими показателями обладают стабилизаторы с УПТ на ОУ, один из вариантов которого показан на рис.2.29. На этом стабилизаторе опорный стабилитрон VD включен в верхнее плечо моста, диагональ которого присоединена к выходу стабилизатора, а вторая - ко входу ОУ. Выходное напряжение стабилизатора равно Uo=Us(R2+R3)/R3. Для защиты регулирующего транзистора VT1 от выхода из строя при коротком замыкании на выходе устройства введены транзистор VT2 и резисторы R4 и R5. При увеличении выходного тока выше допустимого предела падение напряжения на резисторе R5 (около 0,5В) открывает транзистор VT2, в результате чего уменьшается выходное напряжение стабилизатора. При этом резистор R4 защищает выход ОУ от перегрузки при открытом VT2.

Рис.2.29. Компенсационный стабилизатор с ОУ

2.2. Цифровые устройства систем промышленной электроники

Логические элементы

Дешифраторы

Мультиплексоры и демультиплексоры

Триггеры

Постоянные запоминающие устройства

Программируемые логические матрицы

Аналого-цифровые и цифро-аналоговые преобразователи

Компараторы

Логические элементы

Любые цифровые микросхемы строятся на основе простейших логических элементов "НЕ", "ИЛИ", "И". В настоящее время используется несколько технологий построения логических элементов:

транзисторно-транзисторная логика (ТТЛ, TTL)

логика на основе комплементарных МОП транзисторов (КМОП, CMOS)

логика на основе сочетания комплементарных МОП и биполярных транзисторов (BiCMOS)

Простейшим логическим элементом является инвертор, который работает в соответствии со следующей таблицей:

|

Рис. 2.30. Таблица истинности логического инвертора |

|

Рис. 2.31. Изображение логического инвертора на принципиальных схемах. |

Чаще всего существуют не отдельные схемы логического "И", а более сложные схемы, выполняющие одновременно логическую функцию "И" и логическую функцию "НЕ" Таблица истинности и изображение схемы, выполняющей логическую функцию "И-НЕ" изображены на рис 2.32 и 2.33 соответственно:

|

Рис 2.32. Таблица истинности схемы, выполняющей логическую функцию "И-НЕ" |

|

Рис. 2.33. Изображение схемы, выполняющей логическую функцию "И-НЕ" |

Точно также как не существует отдельных схем логического "И", выполненных по технологии ТТЛ, не существует отдельных схем логического "ИЛИ". Таблица истинности и изображение схемы, выполняющей логическую функцию "ИЛИ-НЕ" изображены на рис. 2.34 и 2.35 соответственно:

|

Рис. 2.34. Таблица истинности схемы, выполняющей логическую функцию "ИЛИ-НЕ". |

|

Рис. 2.35. Изображение схемы, выполняющей логическую функцию "ИЛИ-НЕ". |

Построение произвольной таблицы истинности.

Любая логическая схема без памяти полностью описывается таблицей истинности. При построении сложных логических схем с произвольной таблицей истинности используется сочетание простейших схем "И" "ИЛИ" "НЕ". При построении схемы, реализующей произвольную таблицу истинности, каждый выход анализируется (и строится схема) отдельно. Для реализации таблицы истинности при помощи логических элементов "И" достаточно рассмотреть только те строки таблицы истинности, которые содержат логические "1" в выходном сигнале. Строки, содержащие в выходном сигнале логический 0 в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую "1", реализуется схемой логического "И" с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы, описанные в таблице истинности логической "1" подаются на вход этой схемы непосредственно, а входные сигналы, описанные в таблице истинности логическим "0" подаются на вход через иверторы. Объединение сигналов с выходов схем, реализующих отдельные строки таблицы истинности, производится при помощи схемы логического ИЛИ. Количество входов в этой схеме определяется количеством строк в таблице истинности, в которых в выходном сигнале присутствует логическая "1".

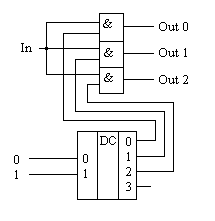

Рассмотрим конкретный пример. Пусть необходимо реализовать таблицу истинности, приведенную на рис. 2.36:

Рис. 2.36. Произвольная таблица истинности

Для построения схемы, реализующей сигнал Out1, достаточно рассмотреть строки, выделенные красным цветом. Эти строки реализуются микросхемой D2 на рис. 2.36. Каждая строка реализуется своей схемой "И", затем выходы этих схем объединяются. Для построения схемы, реализующей сигнал Out2, достаточно рассмотреть строки, выделенные зеленым цветом. Эти строки реализуются микросхемой D3.

Рис. 2.37. Принципиальная схема, реализующая таблицу истинности, приведенную на рис. 2.36.

Дешифраторы

Декодеры (дешифраторы) позволяют преобразовывать одни виды двоичных кодов в другие. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами построения схемы для произвольной таблицы истинности.

Рассмотрим пример построения декодера из двоичного кода в десятичный. Таблица истинности такого декодера приведена на рис. 2.38.

Рис. 2.38. Таблица истинности десятичного декодера

В соответствии с принципами построения произвольной таблицы истинности получим схему декодера. Эта схема приведена на рис. 2.39.

Рис. 2.39. Принципиальная схема двоично-десятичного декодера

Точно так же можно получить схему для любого другого декодера или дешифратора.

Мультиплексоры и демультиплексоры

Мультиплексорами называются устройства, которые позволяют подключать несколько входов к одному выходу. Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. В простейшем случае такую коммутацию можно осуществить при помощи ключей:

Рис. 2.40. Коммутатор (мультиплексор), собранный на ключах

В цифровых схемах требуется управлять ключами при помощи логических уровней. То есть нужно подобрать устройство, которое могло бы выполнять функции электронного ключа с электронным управлением цифровым сигналом.

Рассмотрим таблицу истинности логического элемента "И-НЕ":

Теперь один из входов элемента будем рассматривать как информационный вход электронного ключа, а другой вход - как управляющий. По таблице истинности отчетливо видно, что пока на управляющий вход Y подан логический уровень '0' сигнал со входа X на выход Out не проходит. При подаче на управляющий вход Y логической '1', сигнал, поступающий на вход X, поступает на выход Out. То есть логический элемент "И" можно использовать в качестве электронного ключа. При этом не важно какой из входов элемента "И" будет использоваться в качестве управляющего входа, а какой - в качестве информационного. Остается только объединить выходы элеметов "И" на один выход. Это делается при помощи элемента "ИЛИ". Такая схема коммутатора приведена на рис. 2.41.

Рис. 2.41. Принципиальная схема мультиплексора, выполненная на логических элементах

В этой схеме можно одновременно включать несколько входов на один выход. Однако обычно это приводит к непредсказуемым последствиям. Кроме того, для управления требуется много входов, поэтому в состав мультиплексора включают дешифратор. Это позволяет управлять переключением входов микросхемы на выход при помощи двоичных кодов:

Рис. 2.42. Принципиальная схема мультиплексора, управляемого двоичным кодом

Мультиплексор изображается на принципиальных схемах как показано на рис. 2.43.

Рис. 2.43. Обозначение мультиплексора на принципиальных схемах.

Задача передачи сигнала с одного входа микросхемы на один из нескольких выходов называется демультиплексированием. Демультиплексор можно построить на основе точно таких же схем логического “И” существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор. Cхема демультиплексора приведена на следующем рисунке:

Рис. 2.44. Принципиальная схема демультиплексора, управляемого двоичным

Триггеры

Простейшая схема, позволяющая запоминать двоичную информацию, строится на основе простейших логических элементов, "ИЛИ" или "И". Такая схема, построенная на элементах "И" приведена на рис. 2.45. Вход S (Set) позволяет устанавливать выход триггера Q в единичное состояние при подаче на его вход логического нуля. Вход R (Reset) позволяет сбрасывать выход триггера Q в нулевое состояние при подаче на его вход логического нуля.

Рис. 2.45. Схема простейшего триггера на схемах "И". Входы R и S инверсные (активный уровень'0')

Точно так же можно построить RS триггер и на логических элементах "ИЛИ". Схема RS триггера, построенного на логических элементах "ИЛИ" приведена на рис. 2.46. Единственное отличие будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями.

Рис. 2.46. Схема простейшего триггера на схемах "ИЛИ". Входы R и S прямые (активный уровень '1')

Так как триггер при построении его на различных элементах работает одинаково, то его изображение на принципиальных схемах тоже одинаково. Изображение простейшего триггера на принципиальных схемах приведено на рис. 2.47.

Рис. 2.47. Обозначение простейшего триггера на принципиальных схемах

Схема триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определенные моменты времени, когда все переходные процессы закончены. То есть цифровые схемы требуют синхросигнала. Все переходные процессы должны закончиться за время периода синхросигнала.

Для таких цифровых схем требуются синхронные триггеры. Схема синхронного триггера приведена на рис. 2.48, а обозначение на принципиальных схемах на рис. 2.49.

Рис. 2.48. Схема синхронного триггера на схемах "И"

Рис. 2.49. Обозначение синхронного триггера на принципиальных схемах

В приведенной схеме для записи логического 0 и логической 1 требуются разные входы, что не всегда удобно. Поэтому для запоминания дискретной информации применяются D триггеры. Схема такого триггера приведена на рис. 2.50, а обозначение на принципиальных схемах на рис. 2.51.

Рис. 2.50. Схема D триггера (защелки)

Рис. 2.51. Обозначение D триггера (защелки) на принципиальных схемах

Во всех приведенных схемах синхросигнал работает по уровню, поэтому триггеры называются триггеры-защелки. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рис. 2.52.

Рис. 2.52. Временная диаграмма D триггера (защелки)

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент. отсюда и название - триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту. Схема такого триггера приведена на рис. 2.53, а обозначение на принципиальных схемах на рис. 2.54.

Рис. 2.53. Схема универсального D триггера

Рис. 2.54. Обозначение универсального D триггера на принципиальных схемах

Постоянные запоминающие устройства

Очень часто в различных применениях требуется хранение информации, которая не изменяется в процессе эксплуатации устройства. Это такая информация как программы в микроконтроллерах, начальные загрузчики и BIOS в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах. Практически всегда эта информация не требуется одновременно, поэтому простейшие устройства для запоминания постоянной информации можно построить на мультиплексорах. Схема такого постоянного запоминающего устройства приведена на рис. 2.55.

Рис. 2.55. Схема постоянного запоминающего устройства, построенная на мультиплексоре

В этой схеме построено постоянное запоминающее устройство на восемь одноразрядных ячеек. Запоминание конкретного бита в одноразрядную ячейку производится запайкой провода к источнику питания (запись единицы) или запайкой провода к корпусу (запись нуля). На принципиальных схемах такое устройство обозначается как показано на рис. 2.54.

Рис.2.56. Обозначение постоянного запоминающего устройства на принципиальных схемах

Для того, чтобы увеличить разрядность ячейки памяти ПЗУ эти микросхемы можно соединять параллельно (выходы и записанная информация естественно остаются независимыми). Схема параллельного соединения одноразрядных ПЗУ приведена на рис. 2.57.

Рис.2.57. Схема многоразрядного ПЗУ

В реальных ПЗУ запись информации производится при помощи последней операции производства микросхемы - металлизации. Металлизация производится при помощи маски, поэтому такие ПЗУ получили название масочных ПЗУ. Еще одно отличие реальных микросхем от упрощенной модели, приведенной выше - это использование кроме мультиплексора еще и демультиплексора. Такое решение позволяет превратить одномерную запоминающую структуру в многомерную и, тем самым, существенно сократить объем схемы дешифратора, необходимого для работы схемы ПЗУ. Эта ситуация иллюстрируется следующим рисунком:

Рис. 2.58. Схема масочного постоянного запоминающего устройства

Масочные ПЗУ изображаются на принципиальных схемах как показано на рис. 2.59. Адреса ячеек памяти в этой микросхеме подаются на выводы A0 ... A9. Микросхема выбирается сигналом CS. При помощи этого сигнала можно наращивать объем ПЗУ (пример использования сигнала CS приведен при обсуждении ОЗУ). Чтение микросхемы производится сигналом RD.

Рис. 2.59. Обозначение масочного постоянного запоминающего устройства на принципиальных схемах

Программирование масочного ПЗУ производится на заводе изготовителе, что очень неудобно для мелких и средних серий производства, не говоря уже о стадии разработки устройства. Естественно, что для крупносерийного производства масочные ПЗУ являются самым дешевым видом ПЗУ, и поэтому широко применяются в настоящее время. Для мелких и средних серий производства радиоаппаратуры были разработаны микросхемы, которые можно программировать в специальных устройствах - программаторах. В этих микросхемах постоянное соединение проводников в запоминающей матрице заменяется плавкими перемычками, изготовленными из поликристаллического кремния. При производстве микросхемы изготавливаются все перемычки, что эквивалентно записи во все ячейки памяти логических единиц. В процессе программирования на выводы питания и выходы микросхемы подается повышенное питание. При этом, если на выход микросхемы подается напряжение питания (логическая единица), то через перемычку ток протекать не будет и перемычка останется неповрежденной. Если же на выход микросхемы подать низкий уровень напряжения (присоединить к корпусу), то через перемычку будет протекать ток, который испарит эту перемычку и при последующем считывании информации из этой ячейки будет считываться логический ноль.

Такие микросхемы называются программируемыми ПЗУ (ППЗУ) и изображаются на принципиальных схемах как показано на рис. 2.60. В качестве примера можно назвать микросхемы 155РЕ3, 556РТ4, 556РТ8 и другие.

Рис. 2.60. Обозначение программируемого постоянного запоминающего устройства на принципиальных схемах

Программируемые ПЗУ оказались очень удобны при мелкосерийном и среднесерийном производстве. Однако при разработке радиоэлектронных устройств часто приходится менять записываемую в ПЗУ программу. ППЗУ при этом невозможно использовать повторно, поэтому раз записанное ПЗУ при ошибочной или промежуточной программе приходится выкидывать, что естественно повышает стоимость разработки аппаратуры. Для устранения этого недостатка был разработан еще один вид ПЗУ, который мог бы стираться и программироваться заново.

ПЗУ с ультрафиолетовым стиранием строится на основе запоминающей матрицы построенной на ячейках памяти, внутреннее устройство которой приведено на следующем рисунке:

Рис. 2.61. Запоминающая ячейка ПЗУ с ультрафиолетовым и электрическим стиранием

Ячейка представляет собой МОП транзистор, в котором затвор выполняется из поликристаллического кремния. Затем в процессе изготовления микросхемы этот затвор окисляется и в результате он будет окружен оксидом кремния - диэлектриком с прекрасными изолирующими свойствами. В описанной ячейке при полностью стертом ПЗУ заряда в плавающем затворе нет, и поэтому транзистор ток не проводит. При программировании микросхемы на второй затвор, находящийся над плавающим затвором, подается высокое напряжение и в плавающий затвор за счет туннельного эффекта индуцируются заряды. После снятия программирующего напряжения на плавающем затворе индуцированный заряд остается и, следовательно, транзистор остается в проводящем состоянии. Заряд на плавающем затворе может храниться десятки лет.

Структурная схема постоянного запоминающего устройства не отличается от описанного ранее масочного ПЗУ. Единственно вместо перемычки используется описанная выше ячейка. В репрограммируемых ПЗУ стирание ранее записанной информации осуществляется ультрафиолетовым излучением. Для того, чтобы этот свет мог беспрепятственно проходить к полупроводниковому кристаллу, в корпус микросхемы встраивается окошко из кварцевого стекла.

При облучении микросхемы, изолирующие свойства оксида кремния теряются и накопленный заряд из плавающего затвора стекает в объем полупроводника и транзистор запоминающей ячейки переходит в закрытое состояние. Время стирания микросхемы колеблется в пределах 10 - 30 минут.

Количество циклов записи - стирания микросхем находится в диапазоне от 10 до 100 раз, после чего микросхема выходит из строя. Это связано с разрушающим воздействием ультрафиолетового излучения. В качестве примера таких микросхем можно назвать микросхемы 573 серии российского производства, микросхемы серий 27сXXX зарубежного производства. В этих микросхемах чаще всего хранятся программы BIOS универсальных компьютеров. Репрограммируемые ПЗУ изображаются на принципиальных схемах как показано на рис. 2.62.

Рис. 2.62. Обозначение репрограммируемого постоянного запоминающего устройства на принципиальных схемах

Так так корпуса с кварцевым окошком очень дороги, а также малое количество циклов записи - стирания привели к поиску способов стирания информации из ППЗУ электрическим способом. На этом пути встретилось много трудностей, которые к настоящему времени практически решены. Сейчас достаточно широко распространены микросхемы с электрическим стиранием информации. В качестве запоминающей ячейки в них используются такие же ячейки как и в РПЗУ, но они стираются электрическим потенциалом, поэтому количество циклов записи - стирания для этих микросхем достигает 1000000 раз. Время стирания ячейки памяти в таких микросхемах уменьшается до 10 мс. Схема управления для таких микросхем получилась сложная, поэтому наметилось два направления развития этих микросхем:

ЕСППЗУ

FLASH -ПЗУ

Электрически стираемые ППЗУ дороже и меньше по объему, но зато позволяют перезаписывать каждую ячейку памяти отдельно. В результате эти микросхемы обладают максимальным количеством циклов записи - стирания. Область применения электрически стираемых ПЗУ - хранение данных, которые не должны стираться при выключении питания. К таким микросхемам относятся отечественные микросхемы 573РР3, 558РР и зарубежные микросхемы серии 28cXX. Электрически стираемые ПЗУ обозначаются на схемах как показано на рис. 2.63.

Рис. 2.63. Обозначение электрически стираемого постоянного запоминающего устройства на принципиальных схемах

В последнее время наметилась тенденция уменьшения габаритов ЭСППЗУ за счет уменьшения количества внешних ножек микросхем. Для этого адрес и данные передаются в микросхему и из микросхемы через последовательный порт. При этом используются два вида последовательных портов - SPI порт и I2C порт (микросхемы 93сXX и 24cXX серий соответственно). Зарубежной серии 24cXX соответствует отечественная серия микросхем 558РРX.

FLASH - ПЗУ отличаются от ЭСППЗУ тем, что стирание производится не каждой ячейки отдельно, а всей микросхемы в целом или блока запоминающей матрицы этой микросхемы, как это делалось в РПЗУ.

Рис. 2.64. Обозначение FLASH памяти на принципиальных схемах

При обращении к постоянному запоминающему устройству сначала необходимо выставить адрес ячейки памяти на шине адреса, а затем произвести операцию чтения из микросхемы. Эта временная диаграмма приведена на рис. 2.65.

Рис. 2.65. Временная диаграмма чтения информации из ПЗУ

На рис. 2.65 стрелочками показана последовательность, в которой должны формироваться управляющие сигналы. На этом рисунке RD - это сигнал чтения, A - сигналы выбора адреса ячейки (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода как в единичное, так и в нулевое состояние), D - выходная информация, считанная из выбранной ячейки ПЗУ.

Программируемые логические матрицы

В

настоящие время для реализации логических

устройств используются программируемые

логические матрицы, которые можно

настроить на любую логическую функцию

любой сложности.

Принцип

работы:

Цепь

переменных и их инверсий в соответствии

вертикальными цепями М1 называются

цепями конъюнкции, горизонтальные цепи

М2 - дизъюнкций.

Принцип

работы:

Цепь

переменных и их инверсий в соответствии

вертикальными цепями М1 называются

цепями конъюнкции, горизонтальные цепи

М2 - дизъюнкций.