- •Введение

- •Лабораторная работа 1 основы проектирования цифровых схем в сапр cadence

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •Пакет проектирования сверхплотных и многослойных печатных плат Cadence Allegro.

- •Инструменты Allegro и их функции

- •Этапы проектирования в Allegro.

- •1.Схемный ввод

- •2.Моделирование и анализ схем

- •На этапе моделирования обеспечиваются:

- •3. Размещение компонентов печатной платы

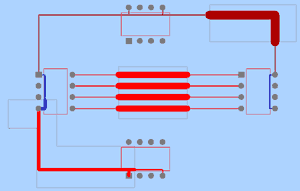

- •4.Трассировка

- •Преимущества трассировки в Allegro:

- •5.Моделирование и анализ пп или имс

- •5.1. Отчет по лабораторной работе должен содержать

- •5.2. Контрольные вопросы к лабораторной работе

- •Перечислите этапы проектирования в Allegro.

- •Опишите маршрут проектирования cadence. Лабораторная работа 2 разработка тактового дерева последовательной схемы

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть Анализ тактового дерева.

- •4. Лабораторное задание и методические указания по его выполнению

- •5. Указания по оформлению отчета и контрольные вопросы

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 3 моделирование работы схемы

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 4 верификация и оптимизация цифровой схемы по временным показателям

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •Компоновка, размещение и трассировка микроэлектронных устройств

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 5 работа с правилами проектирования

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 6 работа с правилами парных контактов

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 7 работа с правилами в иерархическом проектировании

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •4. Лабораторное задание и методические указания по его выполнению

- •5. Указания по оформлению отчета и контрольные вопросы

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Лабораторная работа 8 верификация правил в схеме и в монтажном пространстве

- •1. Общее описание работы

- •1.2. Содержание работы

- •1.3. Используемое оборудование

- •Домашнее задание и методические указания по его выполнению

- •3. Теоретическая часть

- •5.1. Отчет по лабораторной работе должен содержать:

- •5.2. Контрольные вопросы к лабораторной работе

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

ФГБОУВПО «Воронежский государственный технический университет»

Д.Э. Короткевич

АВТОМАТИЗАЦИЯ ПРОЕКТИРОВАНИЯ ЭЛЕКТРОННЫХ СХЕМ В САПР CADENCE:

ЛАБОРАТОРНЫЙ ПРАКТИКУМ

Утверждено Редакционно-издательским советом

университета в качестве учебного пособия

Воронеж 2011

УДК 681.5, 621.37

Короткевич Д.Э. Автоматизация проектирования электронных схем в САПР CADENCE: лабораторный практикум: учеб. пособие / Д.Э. Короткевич. Воронеж: ФГБОУВПО «Воронежский государственный технический университет, 2011. 130 с.

В лабораторном практикуме рассматриваются теоретические и практические сведения для использования САПР CADENCE при проектировании электронных устройств.

Издание соответствует требованиям Государственного образовательного стандарта высшего профессионального образования по направлению 230100 «Информатика и вычислительная техника», специальности 230104 «Системы автоматизированного проектирования», дисциплинам «Автоматизация конструкторского и технологического проектирования», «Автоматизация конструкторского и технологического проектирования микро и наносистем» (бакалавры), «Виды обеспечений САПР» (магистры) студентам очной формы обучения.

Работа выполнена в рамках межвузовской комплексной программы РФ «Наукоемкие технологии образования».

Учебное пособие подготовлено в электронном виде в текстовом редакторе MS Word и содержится в файле АКТП.doc.

Ил. 45. Библиогр.: 3 назв.

Научный редактор д-р техн. наук, проф. Я.Е. Львович

Рецензенты: кафедра вычислительной техники Воронежской государственной лесотехнической академии (зав. кафедрой д-р техн. наук, проф. В.К. Зольников);

д-р техн. наук, проф. О.Н. Чопоров

.© Короткевич. Д.Э., 2011

© Оформление. ФГБОУВПО «Воронежский

государственный технический университет», 2011

Введение

Все знают, что главная деталь каждого компьютера - это процессор, который совершает расчеты. Пользователи требуют все новых возможностей, поэтому производители постоянно выпускают новые и новые модели процессоров.

Каждый новый процессор - это многолетний труд тысяч людей, ведь современный чип содержит сотни миллионов транзисторов, не за горами чипы с миллиардом элементов. Изготовителям приходится иметь дело со слоями материала толщиной всего в несколько молекул. Естественно, нет никакой возможности отлаживать подобный проект на уровне прототипа, необходимо осуществлять проектирование нового процессора с использованием средств компьютерного моделирования. Это многоступенчатый процесс - от создания логической структуры процессора, до разработки корпуса микросхемы и подготовки шаблона для литографии. Все подобные расчеты делаются с помощью специального программного обеспечения (САПР), а создают это программное обеспечение такие компании, как Cadence Design Systems. В каталоге компании Cadence большое количество программных средств для проектирования, таких, как средства проектирования печатных плат, средства высокоуровневой верификации, системы проектирования цифровых и аналоговых схем, средства физической верификации.

САПР Cadence используют сегодня многие ведущие производители микроэлектроники.

Лабораторная работа 1 основы проектирования цифровых схем в сапр cadence

1. Общее описание работы

Цель работы: подготовка исходной информации для моделирования цифровых схем в САПР CADENCE

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в самостоятельном изучении пользовательского интерфейса САПР CADENCE, а также основ проектирования принципиальных схем. Лабораторное задание включает в себя практическое выполнение всех его пунктов.

1.3. Используемое оборудование

Для выполнения лабораторной работы используются программно-аппаратные средства: ПЭВМ класса Pentium стандартной конфигурации, цветной монитор с графическим адаптером SVGA и выше, объем оперативной памяти не ниже 1024 Мб, принтер, ОС Windows XP и выше.

Домашнее задание и методические указания по его выполнению

По методическому руководству ознакомиться с назначением и возможностями САПР CADENCE.

3. Теоретическая часть

Маршрут проектирования CADENCE

Современная СБИС, в частности – типа система на кристалле, может объединять программные и аппаратные средства, в том числе процессорные ядра, программируемую логику, память, интерфейсы, встроенные средства тестирования, аналоговые компоненты. Технология Cadence охватывает практически все уровни разработки сложных систем – от системного уровня, свойственного разработчикам аппаратуры, до уровней логического, схемотехнического и топологического проектирования СБИС, их корпусирования, а также разработки печатных плат, на которых эти СБИС будут монтироваться.

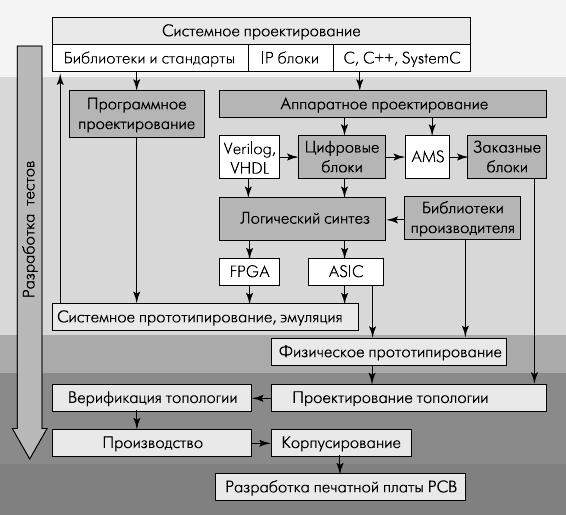

В целом проектирование СБИС в среде Cadence включает следующие этапы (рис.1):

Рис.1. Маршрут проектирования в среде Cadence

Системное проектирование – построение модели системы на высоком уровне абстракции с использованием языков программирования C/C++ и SystemC, разбиение на программные и аппаратные модули, исследование параметров системы, получение спецификаций (набора требуемых параметров) на программные и аппаратные блоки;

Аппаратное проектирование и верификация – разработка на основе спецификации поведенческих моделей отдельных блоков системы с использованием языков Verilog/VHDL, реализация проекта в базисе библиотек производителя ИС, проверка программно-аппаратной реализации на соответствие спецификациям, полученным на системном уровне;

Физическое прототипирование – предварительное размещение элементов, оценка потребляемой мощности, планирование шин питания и иерархии тактовых сигналов, качественная оценка возможных искажений сигнала;

Проектирование и верификация топологии кристалла – разработка топологии заказных блоков, трассировка на уровне ячеек, проверка правил проектирования топологии, экстракция паразитных параметров.

Системное проектирование

На этом этапе определяются функциональные параметры будущей системы на кристалле, ее характеристики, операционная среда, необходимые стандарты и протоколы, разрабатывается модель системы. На системном уровне анализируют характеристики и производительность системы, проверяют архитектуру, определяют способы разрешения конфликтов, оптимизируют алгоритмы и протоколы. При необходимости вносят функциональные изменения в отдельные блоки, перераспределяют программные и аппаратные средства и повторно моделируют работу системы. Для этого предназначены такие инструменты Cadence, как SPW2000 и i-Architect.

Система SPW2000 (signal processing worksystem – рабочая среда обработки сигналов) – это среда проектирования системного уровня. В нее входят средства моделирования системного уровня (включая поддержку моделей на языках С/С++, SystemC, Verilog, VHDL, VerilogAMS, а также созданных в среде Matlab), системные библиотеки элементов, виртуальные генератор и анализатор сигналов, инструментарий разработки фильтров, средства эмуляции системы.

Сама модель строится в удобном специализированном графическом редакторе BDE (Block Diagram Editor) в виде иерархической блок-диаграммы – от общего описания системы до дефрагментации ее на отдельные функциональные блоки. Каждый блок описывается поведенческой моделью и набором требуемых характеристик – спецификацией блока. Разработчику совершенно необязательно создавать модели всех блоков – библиотека SPW2000 содержит более 3500 модулей. Среди них – коммуникационные системы сотовой связи WCDMA, cdma2000, IS-95, GSM/GPRS/HSCSD/EDGE, IS-54/136; беспроводные сети стандартов IEEE802.11a/b, HiperLAN/2, Bluetooth; телевизионные системы стандартов DVB-T, ISDB-T, NTSC; модемы физических линий ADSL; библиотеки высокочастотных систем и радаров, MPEG ½-кодеки, оптические системы, датчики, системы компрессии и т.д.

Кроме библиотечных модулей SPW2000, разработчик может использовать собственные системные модели на языках С/C++/SystemC и модели, созданные в среде Matlab. Принципиально, что при моделировании система может включать блоки, описанные на разных уровнях представления – как на системном, так и на уровне регистровых передач (RTL-уровень) на языках VHDL/Verilog (т.е. уже "готовые" блоки). Таким образом, в системной модели можно использовать непосредственно описания IP-блоков, включая прямую поддержку IP-ядер для FPGA компании Xilinx. Это существенно сокращает число циклов проектирования и повышает вероятность успешной реализации проекта с первого раза. Для работы с библиотеками IP-блоков, их пополнением из on-line-библиотек других компаний через Интернет, а также для поиска требуемых IP-блоков по заданным характеристикам служит платформа i-Architect.

Средства SPW2000 позволяют моделировать работу всей системы в целом или ее отдельных блоков. При этом можно использовать реальные сигналы и данные – например, промоделировать передачу изображения через цифровой канал связи.

Платформа SPW использует алгоритмы вычислений с плавающей точкой. Их преобразование в алгоритмы с фиксированной точкой, необходимые для аппаратной реализации системы, выполняет пакет HDS2000.

Он содержит специальную библиотеку стандартных блоков, а также поддерживает такие опции SPW, как виртуальный генератор/анализатор сигналов и логический анализатор. Именно HDS позволяет из структурного описания системной модели генерировать ее описание на языках Verilog/VHDL. В результате проектирования на системном уровне формируются детальное описание архитектуры системы, спецификации отдельных программных и аппаратных блоков и их функциональное описание на языках C/C++ и SystemC (рис.2). Последующий этап программно-аппаратного проектирования при необходимости могут проводить уже другие группы разработчиков

Аппаратное проектирование и верификация.

На уровне аппаратного проектирования разрабатывается HDL-модель СБИС, формируется ее схема в базисе библиотечных элементов конкретного производителя ИС и создается список цепей (netlist) для последующего топологического проектирования. Генерация схем цифровых блоков происходит преимущественно автоматически. Аналоговые узлы и модули смешанной обработки проектируются в интерактивном режиме с использованием средств Cadence SPICE и Spectre.

.

Рис.2. Последовательность этапов разработки на системном уровне.

Основа аппаратного проектирования в системе Cadence – платформа Incisive. Она представляет собой единую среду программно-аппаратного проектирования, отладки, верификации и генерации тестов для цифроаналоговых СБИС от системного уровня до уровня RTL. Incisive поддерживает языки Verilog, VHDL, SystemC, библиотеку SCV для SystemC и PSL/Sugar assertions. Наряду с этим Incisive предоставляет разнообразные средства отладки, в том числе – на уровне транзакций, и унифицированный генератор тестов.

При необходимости платформу Incisive можно дополнить различными элементами, включая выборочное ускорение, аналоговое и смешанное моделирование с ВЧ_элементами, средствами разработки и отладки алгоритмов, аппаратным ускорителем моделирования Palladium. Использование ускорителя Palladium совместно с платформой Incisive позволяет в 100 раз повысить производительность аппаратного проектирования по сравнению со стандартным маршрутом разработки, сократить на 50% цикл разработки тестов и на 25% – время отладки.

Инструментом реализации проекта в базисе библиотечных элементов производителя СБИС служат средства логического синтеза BuildGates. Этот пакет предназначен для логического синтеза схемы с учетом физических и технологических особенностей проектируемого кристалла. В дальнейшем полученный в результате синтеза список цепей может служить входной информацией для трассировки топологии кристалла.

Средства Cadence позволяют вести и разработку заказных модулей СБИС, главным образом – аналоговых блоков и модулей смешанной обработки сигнала. Для этого, в частности, предназначен пакет AMS (analog mixed_signal). С помощью этой многоуровневой платформы можно разрабатывать, моделировать и отлаживать схему от системного уровня вплоть до выхода на топологическое проектирование.

По завершении этапа аппаратного проектирования происходит верификация и моделирование SоC с использованием различных уровней представления.

Физическое прототипирование

Физическое прототипирование предназначено для аппроксимации основных характеристик кристалла высокой степени интеграции и их оптимизации до трудоемкого этапа трассировки топологии СБИС и последующей экстракции ее параметров. Используемый на этом этапе виртуальный прототип СБИС позволяет с точностью до 90% определить ее основные параметры: временные характеристики, паразитные параметры, занимаемую площадь, потребляемую мощность и др. Весь комплекс задач по физическому прототипированию решает платформа Cadence First Encounter Ultra. Она позволяет произвести физический синтез до 2 млн. ячеек, размещение элементов на кристалле, пробную трассировку, быстрый анализ с 2,5D_экстракцией, анализ задержек и временных характеристик, анализ качества. Платформа включает средства физической оптимизации, автоматическое разбиение кристалла, присвоение выводов; иерархический синтез сигнала синхронизации; планирование сетки питания; содержит интерфейсы с ведущими средствами разработки топологии и удобный пользовательский интерфейс. С помощью First Encounter Ultra можно быстро – в течение одного дня – и эффективно прототипировать сложные цифровые системы, включающие до нескольких миллионов вентилей.

Проектирование и верификация топологии кристалла

Как правило, современные SoC содержат и цифровые, и аналоговые блоки. Для разработки топологии цифровых блоков при технологиях до 0,18 мкм традиционно использовались средства автоматической трассировки Silicon Ensemble от Cadence. Однако сегодня массовыми становятся технологические нормы 0,13 мкм и менее. Для таких технологий Cadence предлагает современные средства разработки топологии цифровых ИС NanoRoute.

Для трассировки заказных аналоговых блоков предназначен топологический редактор Virtuoso_XL. Он имеет удобный пользовательский интерфейс, поддерживает иерархические проекты и параметризацию ячеек, легко интегрируется с ведущими средствами проектирования различных уровней. Встроенный язык управления SKILL позволяет настроить процесс проектирования топологии под требования заказчика.

По окончании разработки топологии ее необходимо проверить на соответствие правилам проектирования и произвести экстракцию паразитных параметров с учетом реального размещения элементов и проводников на кристалле. Для решения всего комплекса задач верификации топологии ИС предназначены пакеты Diva, Dracula, Assura. Они содержат средства проверки правил проектирования (DRC), позволяют сравнить разработанную топологию со списком цепей или принципиальной схемой (LVS). С помощью средств верификации из топологии можно экстрагировать паразитные параметры (RCX) и временные задержки, а затем с их учетом промоделировать схему.

Проектирование СБИС с использованием современных технологий (0,13 мкм и менее) становится невозможным без детального анализа разработанной топологии, учета влияния на временные характеристики кристалла наводок и помех на проводниках и разброса напряжения питания на ячейках. Для решения комплекса этих задач могут быть использованы средства Cadence, ориентированные на нанотехнологии: Fire&Ice – 3D_экстракция паразитных параметров из топологии кристалла; Celtic – быстрая и эффективная система анализа перекрестных помех на проводниках и, как следствие, искажений сигналов; VoltageStorm – инструмент учета влияния разброса напряжения питания на временные характеристики системы.

Современные технологии Cadence основаны на открытых базах данных Open Access и легко конфигурируются в сквозной маршрут проектирования. Именно поэтому программные средства Cadence широко используются ведущими компаниями в России и за рубежом.

Решения CADENCE для проектирования печатных плат

Комплексные физические и электрические ограничения, плотная упаковка компонентов, да и всё более жесткие требования, предъявляемые высокоскоростными технологиями к печатным платам – это всего лишь некоторые из тех вещей, которые увеличивают сложность сегодняшних проектов. Разработчику чрезвычайно нужна возможность легко определять, управлять и проверять ограничения на ширину проводников, на зазоры, на длину трасс – так же, как и свойства критических высокоскоростных сигналов – на каждом шаге выполнения проекта. В то же время разработчик должен быть уверен в том, что окончательный проект печатной платы полностью соответствует как исходным требованиям к ней, так и параметрам, связанным с её изготовлением, монтажом и тестированием.

Решения Cadence для проектирования печатных плат – это законченная среда для разработки, которая позволяет реализовать эти задачи с учётом всех особенностей производства. Среда разработчика включает в себя всё необходимое для создания проекта – от идеи до готовой продукции, с полностью интегрированным циклом проектирования, включая схемный ввод, утилиты выбора компонентов, редактор печатной платы, автоматический/интерактивный трассировщик, а также интерфейсы для производства и связь с механическими САПР. Единая архитектура базы данных, модель использования и библиотека предоставляют полностью масштабируемые решения для проектирования печатных плат и в линейке Cadence OrCAD, и в продуктах Allegro, давая пользователю возможность расти и расширяться по мере необходимости, от проекта к проекту, с ростом их сложности. Результат – увеличение продуктивности разработчиков, сокращение цикла проектирование, существенно более быстрый выход на массовое производство.

Программа трассировки печатных плат SPECCTRA

Платформа Cadence Allegro для проектирования системных схем позволяет осуществлять совместную разработку высокопроизводительных (высокочастотных) схем на уровнях внутренних соединений ИС, корпусирования ИС и печатных плат. Уникальная единая методология совместного проектирования этой платформы позволяет оптимизировать соединения на всех уровнях системы между буферами ввода/вывода и внутренние цепи ИС корпусами и печатными платами для уменьшения количества этапов макетирования, снижения затрат и сокращения циклов проектирования.

Система Allegro, базирующаяся на задании ограничивающих условий, отличается расширенными возможностями ввода схем, контроля целостности сигнала и физической реализации. Благодаря этому пакетам компании-разработчики ИС получают возможность сократить время, требуемое для запуска новых устройств в эксплуатацию, а производители системных печатных плат сокращают циклы разработки новых образцов для снижения периода окупаемости. Благодаря поддержке платформ Cadence Encounter и Virtuoso , методология совместного проектирования Allegro обеспечивает эффективное взаимодействие разработчиков на всех этапах.

Программа трассировки печатных плат Cadence SPECCTRA, входящая в состав универсальной платформы для проектирования электронных устройств, является лидером на рынке решений для автоматической и интерактивной трассировки. Для эффективного решения задач, связанных с трассировкой как простых схем, так и печатных плат с высокой плотностью компонентов с учетом сложных и высокоскоростных правил проектирования, система трассировки печатных плат SPECCTRA использует мощные алгоритмы, основанные на бессеточном алгоритме. В результате область трассировки используется максимально эффективно, что влечет повышение продуктивности и сокращение циклов проектирования.

Программа трассировки печатных плат SPECCTRA входит в состав таких решений как редактор печатных плат Cadence Allegro, программ для пакетирования ИС, программы для разработки печатных плат Allegro PCB SI 610 (PCB Design Expert). Помимо этого SPECCTRA интегрирована в большинство наиболее популярных систем автоматизированного проектирования печатных плат.

При необходимости разработать многослойную плату с высокой плотностью компонентов программа для автоматической трассировки SPECCTRA.

Помимо функции автоматической трассировки, эта программа представляет собой целостную среду разработки схем соединений с интерактивным и автоматическим размещением компонентов, а также бессеточной 45-градусной интерактивной и автоматической трассировкой

Возможности программы

Поддержка операционных систем Windows, UNIX и Linux с возможностью переноса лицензии при смене платформы.

Поддержка высокоскоростных правил/ограничивающих условий для контроля задержек, перекрестных помех, полного сопротивления; дифференциальных пар, и распределения цепей, включая создание виртуальных выводов.

Трассировка в реальном масштабе времени с поддержкой системы задания правил, учитывающих задержки, перекрестные помехи, полные сопротивления, распределения цепей и работу с дифференциальными парами.

Автоматическое экранирование цепей с формированием соединений методом "сшивания" в автоматическом режиме

Полная поддержка трассировки с изгибами под углом 45 либо 90 градусов

Полная поддержка структур Microvia (микропереходов)

Трассировка с учетом наборов слоев.

Рекурсивное сглаживание 900 углов позволяет достигать результатов, неотличимых от работы в ручном режиме.

Возможность трассировки и размещения компонентов в интерактивном режиме

Размещения компонентов в автоматическом режиме

Полная интеграция с Allegro PCB Editor, Allegro Package Designer 610 и Allegro PCB SI 610

Имеется интерфейс для сопряжения с приложениями Mentor Board Station и Mentor PowerPCB

Программа SPECCTRA позволяет реализовать требуемое распределение цепей, контроль задержек и перекрестных помех, трассировку с учетом наборов слоев, а также выполнение особых требований к геометрии современных высокоскоростных схем.

Топология цепей

Распределение цепей определяет порядок трассировки (соединения) контактов цепи и даже вставляет промежуточные точки трассировки (t-образное соединение). Это позволяет создавать ограничивающие условия для каждого сегмента цепи для максимально точного контроля соединений даже в случаях, когда цепь содержит дискретное устройство (например, согласующий резистор). Для каждой цепи можно задать ограничения на ее длину или задержку распространения сигнала, что позволяет контролировать длину каждого проводника. Также существует возможность определения минимальной либо максимальной задержки вносимой проводником или определения его длины для того, чтобы конкретный сигнал гарантированно достиг "своей точки назначения" в пределах заданного периода времени.

Перекрестные помехи

Перекрестные помехи ограничиваются с помощью геометрических или "параллельных" правил. Пользователь может устанавливать допустимые значения зазоров и длин, а программа SPECCTRA автоматически разобьет параллельные линии на заданные длины и разнесет их на заданные расстояния. Можно также создавать таблицы допустимых соответствий зазор-длина для более точного представления модели перекрестных помех. Перекрестные помехи можно снизить путем оценки геометрического либо физического расположения проводников, а также электрических свойств сигналов, передаваемых по проводникам. При этом также учитывается шум, генерируемый проводниками одного слоя и прилегающих слоев (тандем). Совокупные шумовые перекрестные помехи контролируются комплексными "шумовыми" правилами, учитывающими электрические характеристики проектируемой платы. Пользователь может определить максимальное значение совокупных перекрестных помех в милливольтах, допустимое для каждого класса или цепи. Программа SPECCTRA выполняет динамический расчет максимальных совокупных шумовых перекрестных наводок при трассировке путем сложения всех параллельных и спаренных проводников.

Рис.3. Распределение цепей без задания "шумовых" ограничений

Рис.4. Распределение цепей с заданием "шумовых" ограничений (введена послойная и тандемная таблицы допустимых значений длина/расстояние)

Формируемые отчеты включают в себя спаренные шумовые характеристики, полученные при анализе геометрического или физического расположения проводников и электрических свойств сигналов. При расчетах учитывается шум, генерируемый сигналами одного слоя либо на прилегающих слоев (тандем). При анализе генерируются сообщения о возможных ошибках временного согласования, в которые входят значения нарушений минимальных и максимальных длины проводников. Вся эта информация записывается в файл отчета и отображается в графической форме.

Наборы слоев

Под трассировкой с учетом наборов слоев подразумевается объединение слоев в трассировочные наборы для более точного контроля электрических характеристик сигналов. При трассировке цепей либо шин с контролем полного сопротивления может потребоваться переход с одного слоя на другой. Отсутствие контроля данных переходов может повлечь изменения полного сопротивления в зависимости от местоположения нового слоя в структуре печатной платы. Для решения этой проблемы выбранный целевой слой (слои) должен иметь такое же полное сопротивление, как и исходный слой. Функция трассировки с учетом наборов слоев позволяет определять наборы, пригодные для трассировки цепей (или классов) и шин. Эти характеристики обычно связаны с аналогичными значениями полного сопротивления конкретных слоев в наборе. Слои, не входящие в выбранный набор, для трассировки указанных цепей недоступны.

Дифференциальные пары, экранированные цепи и правила для областей (комнат)

Программа SPECCTRA также обладает способностью гибкой обработки особых требований к геометрии высокоскоростных печатных плат. Для трассировки дифференциальных пар пользователь может определить значение зазора между двумя проводниками, а все остальное проделает программа автоматической трассировки.

Рис.5. Программа SPECCTRA автоматически трассирует дифференциальные пары в соответствии с геометрическими и "параллельными" принципами

Программа SPECCTRA осуществляет интеллектуаль-ную трассировку дифференциальных пар с использованием переходных отверстий или без таковых в соответствии с заданными критериями минимизации длины.

Автоматическое экранирование применяется для снижения шума в чувствительных к нему цепях. Резкое уровней сигналов привело к тому, что экранирование стало неотъемлемым элементом разводки высокоскоростных плат. Для достижения нужного эффекта экранирующая цепь должна быть соединена с экранным слоем заземления через равные промежутки для эффективного поглощения блуждающих шумов. Программа SPECCTRA не только автоматически генерирует экраны вокруг экранируемых цепей, а и привязывает экранирующий проводник к выбранному экранному слою заземления путем автоматической вставки переходных отверстий через указанные интервалы.

Рис.6. Экранированным сигналам автоматически присваиваются экраны с созданием сквозных перемычек через заданные интервалы, которые связывают экран со слоем заземления

Отдельные правила формирования разводки платы могут применяться в различных областях. Например, пользователь может повысить плотность трассировки с помощью задания меньших зазоров в области разъема, в то время как в других областях будет допустима меньшая плотность (большие зазоры).

Рис.7. Изменение толщины печатных проводников в зависимости от участка (комнаты), по которым они проходят

Сложные физические правила

Функция создания сложных физических правил программы SPECCTRA позволяет контролировать электрические параметры, отслеживать перекрестные помехи и нарушения заданных длин проводников в соответствии с сегодняшними жесткими требованиями к большим печатным платам. В контроль электрических параметров входит гибкое назначение конкретных правил каждому элементу проекта. Пользователь может определять правила, необходимые для соблюдения характеристик электрических класса устройств уникальные для каждого слоя: типы переходных отверстий, ширины проводников или либо набора соединений (частей электрических цепей между двумя контактными площадками). Благодаря этой функции становится возможным использование переходных отверстий большего диаметра для расширения диапазона предельно допустимого тока в соответствии с требованиями к цепям земли и питания. Таким образом, достигается экономия пространства платы, так как "большие" переходные отверстия используются только для указанных сигналов. Более того, "совмещение" импеданса сигналов можно улучшить путем назначения различных правил ширины проводников и зазоров между ними для различных слоев платы.

Внешние слои обычно отличаются более высоким общим сопротивлением, поэтому для них назначается увеличенная ширина дорожек. Внутренние слои, напротив, обычно отличаются меньшим импедансом, поэтому для них назначается уменьшенная ширина дорожек для достижения одинакового импеданса с внешними слоями. "Совмещение" импеданса также можно улучшить путем распределения трассируемых цепей по определенным слоям либо парам слоев.

Микропереходы

Учитывая требования, предъявляемые к современным многослойным платам, многие компании активно рассматривают преимущества увеличения количества слоев печатных плат с использованием новых технологий производства для существенного снижения габаритных размеров и улучшения характеристик сигналов. Одним из главных требований к новым технологиям наращивания слоев является поддержка сложных структур переходных отверстий. Возможность создания микропереходов (Microvia) программы SPECCTRA была разработана с использованием передовой технологии ALIVH компании Matsushita. Эта возможность включает поддержку нескольких переходов (т.е. кластера либо массива переходов), что позволяет увеличить диапазон предельно допустимых токов для широких дорожек. Технология формирования многоуровневых переходов позволяет размещать "глухие" и "замурованные" переходные отверстия в точке с одними и теми же X-,Y-координатами на различных слоях платы. Улучшенное расстановка фанаутов позволяет использовать "глухие" и "замурованные" переходные отверстия под SMD-контактными площадками. При выборе функции Microvia появляется возможность создания многоуровневых переходов под контактными SMD-площадками даже в местах, где площадки находится друг напротив друга на противоположных сторонах платы (рис.8).

Рис. 8. Пример использования "глухих" и "замурованных" отверстий

Сложные правила формирования структуры печатной платы

Программа SPECCTRA обеспечивает возможность применения "глухих" либо "замурованных", поверхностных проводных соединений, а так же размещения переходных отверстий под контактными площадками на поверхности платы согласно требованиям современных стандартов керамических корпусов компонентов печатных плат и компонентов. Для обеспечения переходов между слоями программа автоматически использует "глухие" или "замурованные" переходные отверстия. Зазоры между переходами различных слоев контролируются таким же образом, как и в переходных отверстий одного слоя. Переходное отверстие можно разместить под SMD-контактной площадкой в исходной точке либо в ближайшей узловой точке от исходной. Также возможен контроль полного соблюдения границ SMD-контактной площадки при размещении переходов под ней. В случае если "форма" перехода в слое контактной площадки выходит за ее пределы, размещение перехода становится невозможным.

Поддержка поверхностного проводного соединения обеспечивает трассировку плат с использованием бескорпусной многовыводной элементной базы. Точки припайки (дополнительные контактные площадки) размещаются и автоматически трассируются дискретными проводниками, проходящими от каждой установленной дополнительной контактной площадки к контактным площадкам микросхемы, смонтированной на печатной плате. Пользователь может определить тип устанавливаемых контактных площадок и максимально допустимое расстояние между ними и контактными площадками компонента.

Подготовка к производству

Функция подготовки к производству программы SPECCTRA позволяет существенно увеличить выход годных печатных плат благодаря команде "разнесения", автоматически увеличивающей зазоры между проводниками в зависимости от имеющегося запаса свободного места. Эта функция также выполняет сглаживание изгибов под углом 45 градусов и добавляет контрольные точки после автотрассировки (рис. 9 - 10).

Рис.9. До сглаживания Рис.10. После сглаживания

Автоматическое "разнесение" проводников используется для повышения технологичности плат путем изменения расположения проводников для увеличения пространства между проводниками и контактами, проводниками и SMD-контактными площадками, а также соседними сегментами проводников. Пользователь может гибко определять диапазон значений зазоров либо использовать значения по умолчанию. Прямые углы автоматически заменяются диагональными срезами с использованием заданного пользователем значения отступа либо значения по умолчанию. Сглаживание прямых углов может применяться либо ко всей плате, либо к отдельным слоям с указанием одного значения либо диапазона значений отступа. Функция подготовки платы к производству позволяет автоматически использовать оптимальное значение отступа в пределах выбранного диапазона от большего к меньшему значению.

Вставка контрольных точек

Функция вставки контрольных точек автоматически добавляет контролепригодные переходные отверстия либо контактные площадки, служащие контрольными точками. Расстановка контрольных точек может осуществляться с верхней, нижней или с обеих сторон печатной платы, позволяя применять измерительные приборы с односторонними и створчатыми рабочими элементами. Пользователь может выбирать методику вставки контрольных точек в соответствии с производственными потребностями. Для того чтобы избежать необходимости дорогостоящих модификация испытательных стендов, контрольные точки могут "фиксироваться". Ограничивающие условия для контрольных точек учитывает типы поверхности рабочих элементов измерительных приборов, размеры переходных отверстий, сетки переходных отверстий, а также минимальные расстояния между их центрами.

Редактор размещения SPECCTRA

Редактор размещения SPECCTRA позволяет быстро расположить компоненты на плате с одновременной оценкой свободного пространства, логики прохождения сигналов и узких мест на плате до начала трассировки.

Режим перемещения (Move mode) позволяет отзеркаливать (перемещать на другую сторону) компоненты, вращать, выравнивать, расталкивать и перемещать их по одиночке либо в составе группы.

В режиме размещения с подсказкой (Guided-place mode) выбирается компонент с наиболее высокой связностью и помещается в оптимальную точку на плате (рассчитывается программой) в соответствии с правилами расположения элементов либо ограничивающими условиями. После определения местоположения компонента пользователь может подтвердить либо отказаться от предложенной позиции. Расположение компонентов может также осуществляться путем непосредственного ввода их пространственных координат. Эта возможность оказывается особенно полезной при расположении разъемов и компонентов с фиксированными позициями.

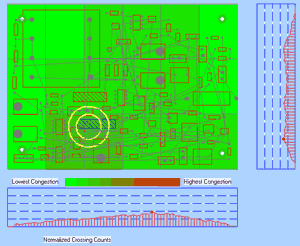

Анализ плотности компонентов позволяет оценить степень насыщенности платы благодаря наглядной графической форме представления результатов. Печатная плата представляется в виде цветной карты, на которой выделяются перенасыщенные места по сравнению с областями с меньшей плотностью элементов. Это позволяет выявить области, требующие ручной корректировки расположения компонентов для борьбы с перенасыщенностью и улучшения трассировки.

Рис.11. Размещение с подсказкой

Авторазмещение в SPECCTRA

Функция авторазмещения программы SPECCTRA основана на бессеточном принципе и поддерживает платы с большим количеством слоев трассировки (до 256) и неограниченным количеством выводов компонентов. Данная функция позволяет размещать компоненты без определения сетки и длительных настроек для компонентов различной формы, требующих значительных временных затрат. Функция авторазмещения (Autoplacement) позволяет расставлять некоторые компоненты автоматически, а некоторые интерактивно. Функция позволяет резервировать пространство (создавать "комнаты") для подвода раздельного питания, задавать ограничивающие условия по высоте, рассеиванию тепла либо разделению аналоговых электрических схем, схем процессора, схем памяти, TTL-и ECL-схем. Компоненты могут одновременно размещаться по обеим сторонам печатной платы с выравниванием SMD-компонентов с одинаковой ориентацией. Правила зазоров между компонентами могут определяться стороной платы, типом компонента либо компонентом, что позволяет выполнить требования, задаваемые станками автоматической расстановки компонентов.

Рис.12. Авторазмещение компонентов

Трассировщик

Трассировщик представляет собой новое слово в трассировке печатных плат благодаря своим продвинутым функциям трассировки и редактирования.

При трассировке новых проводников функция огибания (plowing) позволяет автоматически создавать проходы между существующими проводниками и прокладывать трассы в обход выводов. Функция перемещения (shoving) позволяет перемещать сегменты проводников либо переходные отверстий поверх существующих трассы других переходных отверстий. Функция предварительной оценки (ghosting) позволяет быстро оценивать варианты трассировки по принципу "что будет, если:" . При захвате сегмента проводника либо переходного отверстия курсором, прилегающий проводник отводится в сторону, с динамическим отображением этого процесса. Перед тем, как остановиться на окончательном варианте конфигурации пользователь имеет возможность оценить скорректированные варианты трассировки. Кроме того, многоуровневая функция отмены позволяет быстро вернуться к предыдущим вариантам трассировки.

Расширенные функции редактирования

В высокоплотных и многослойных платах поиск точек допустимых для расстановки переходных отверстий крайне затруднителн SPECCTRA позволяет размещать переходные отверстия двойным щелчком мышью в выбранной точке. Если в данной точке размещение переходного отверстия возможно, программа автоматически раздвигает проводники на различных слоях платы по мере необходимости. В противном случае SPECCTRA выводит сообщение о нарушении правил проектирования и отображает доступные точки размещения переходных отверстий в прилегающих областях. Функция копирования трасс (трассировка по подобию) существенно облегчает построение шин благодаря возможности копирования существующей трассы для завершения невыполненных шинных соединений. Новая трасса использует ту же топологию что и исходная с автоматической подгоном длины проводников (стоит отметить, что для трассировки в общем случае достаточно просто выделить несколько цепей при трассировке: в этом случае они будут оттрассированы совместно. В автоматическом режиме так же возможна трассировка шин, для чего предусмотрены опции команды объединения цепей в шины).

SPECCTRA также позволяет использовать разные углы изгибов, которые можно настроить в соответствии с требованиями проекта. Укажите 45-градусные, 90-градусные либо произвольные изгибы, и программа автоматически будет использовать изгибы согласно вашим предпочтениям. Функция оптимизации позволяет избавиться от лишних точек перегиба, созданных в процессе редактирования. После выбора нужной области, либо всей платы функция оптимизации скорректирует трассировку для улучшения технологичности платы.

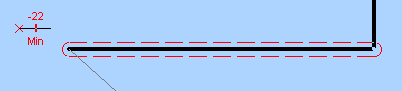

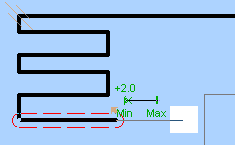

Правила длин и ограничивающие условия по тактировке

Благодаря возможности задания "высокоскоростных" правил, SPECCTRA делает трассировку цепей в соответствии с ограничениями по временным задержкам крайне простой, что достигается заданием минимально и максимально допустимых длин. Имеется возможность динамического применения правил минимальной и максимальной длины проводников. Две прогрессивные методики графического отображения помогают выполнять эффективную трассировку цепей с огранивающими условиями по временным задержкам (рис. 13-14).

Рис.13. Ограничение длины по минимальной временной задержке

Рис.14. Ограничение длины по минимальной и максимальной временным задержкам

Первая представляет собой "цветовой" измеритель, отображающий подробную информацию о длине проводника, которая динамически обновляется во время интерактивной трассировки. Этот цвет указывает, соответствует ли проводник ограничениям по минимальной и максимальной длине. Значение индикатора определяется путем добавления отрассированной длины к оставшейся Манхетеновской длине до точки назначения. Эта моментальная обратная связь позволяет отслеживать ход трассировки и контролировать остаток длины, доступной для завершения соединения.

Вторая - представляет более полное отображение условий соблюдения ограничения на временные задержки. При соблюдении ограничений по максимальной длине вокруг текущей позиции курсора и целевого вывода отображается зеленый многоугольник. Тем не менее, этот многоугольник не содержит информации о приближении к границами максимально допустимой длины. Красный многоугольник отображает область, внутри которой нарушается ограничение на минимальную длину. Первые и второй вариант контроля могут использоваться совместно.

Рис. 15 а. Примеры отображения областей с ограничениями

Возможности программы SPECCTRA

Трассировка до 256 сигнальных уровней

Настоящая бессеточная или сеточная трассировка.

Расстановка фанаутов.

Трассировка шин памяти (для SMD-контакных площадок либо сквозных)

Пошаговое многопроходное сглаживание прямых углов изгибами под 45 градусов.

Задание типа переходных отверстий для цепей или классов цепей.

Задание зазоров для цепей или классов цепей.

Послойное задание правил для цепей классов цепей.

"Мягкие" и "жесткие" границы допустимых зон трассировки.

Трассировка с учетом наборов слоев

Автоматическое "разнесение" проводников

Автоматическая генерация контрольных точек

Поддержка "глухих", "замурованных" и микро- переходов

Расстановка переходных отверстий под SMD-контактными площадками

Автоматическая поверхностная проводная трассировка

Автоматическое свапирование эквивалентных секций и выводов.

Контроль "параллельности" проводников

Контроль суммарного шума

Контроль максимальной/минимальной/совпадающей задержки и длины

Возможность удлинения цепи, определяемыми пользователем способом.

Автоматическая/интерактивная трассировка дифференциальных пар

Правила/зазоры для отдельных областей (комнат)

Экранирование цепей.

Создание виртуальных выводов для контроля топологии.

Возможности редактора размещения компонентов

Проверка правил проекта в интерактивном режиме

Размещение

Режим размещения с подсказкой

Зеркалирование, поворот, выравнивание и перемещение отдельных компонентов либо групп компонентов

Анализ плотности размещения

Размещение компонентов в указанные координаты.

Возможности автоматического размещения

Автоматическое размещение компонентов с обеих сторон платы

Правила размещения для отдельной стороны, компонента и/или типа компонента.

Автоматическое свапирование эквивалентных секций и выводов.

Автоматическая кластеризация (совместная расстановка группы компонентов)

Возможности интерактивной трассировки

Функции огибания и расталкивания препятствий, а так же предварительная оценка результатов

Интерактивный поиск пригодных для вставки точек переходных отверстий.

Проверка правил проектирования в интерактивном режиме

Автоматическая оптимизация трасс

Интерактивный счетчик, отображающий ограничения по длине

Общий индикатор соблюдения ограничивающих условий

Цветная индикация с обратной связью

Трассировка нескольких цепей (шин)

Автоматическая трассировка одиночных цепей