Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Электронный конспект лекций (ЦиМПУ)

.pdf

- RESIN |

(RESET IN) |

– вход сигнала сброса МП в начальное состояние. |

|

Сигнал может поступать в любое время по команде оператора. Автоматически формируется при включении питания (рисунок 3.4). Под его воздействием сбрасываются регистры PC и IR, триггеры разрешения прерывания, подтверждения захвата и др.;

- RESET – выходной сигнал сброса для внешних модулей системы, привя-

занный к тактовым импульсам фазе.

CLK, т. е. отличающийся от сигнала

RESIN

по

3.2.9 Синхронизация и последовательность действий МП

При естественном следовании команд МП, начав работу, выбирает из памяти и выполняет одну команду за другой, пока не дойдет до команды HLT «останов». Процессы выполнения команд подчиняются строгой последовательности действий.

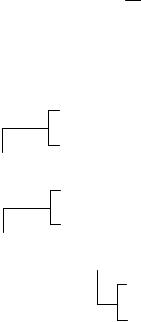

Выборка и выполнение одной команды образуют командный цикл (КЦ). Каждый КЦ состоит из одного или нескольких машинных циклов (МЦ). В свою очередь машинный цикл делится на то или иное число тактов Т, число которых зависит от типа машинного цикла. На рисунке 3.8, а показан КЦ, состоящий из трех МЦ.

|

|

|

|

КЦ |

|

|

|

|

b1 |

N – 2 |

||

|

М1 |

|

М2 |

|

М3 |

|

b2 |

N – 1 |

||||

Т1 |

Т2 |

Т3 |

Т4 |

Т1 |

Т2 |

Т3 |

Т1 |

Т2 |

Т3 |

|

b3 |

N |

|

|

|

|

а) |

|

|

|

|

б) |

|

||

Рисунок 3.8 – Циклы и такты МП (а) и пример размещения команды в памяти МПС(б)

МП имеет следующие типы МЦ:

-выборки кода команды OF (от англ. Opcode Fetch);

-чтение из памяти MR (от англ. Memory Read);

-записи в память MW (от англ. Memory Write);

-чтение из ВУ IOR (от англ. Input-Output Read);

-записи в ВУ IOW (от англ. Intput-Output Write);

-подтверждение прерывания INA (от англ. Interrupt Acknowledge);

-освобождения шин BI (от англ. Bus Idle);

-останов HALT.

191

Каждое обращение к памяти или ВУ требует машинного цикла для передачи байта в МП или из него. Обращает на себя внимание отсутствие МЦ, связанных с выполнением суммирования, вычитания, сдвига и т. п., так как подобные операции, будучи внутренними, т. е. не требующими обращений к модулям МПС по системным шинам, выполняются быстро, и для них достаточно добавлений отдельных тактов в машинные циклы, предназначенные для передачи данных.

Вначале каждого МЦ генерируются сигналы состояния, идентифицирующие тип цикла и действующие в течение всего цикла. Сигналы, реализующие тот или иной МЦ, генерируются блоком управления МП на основании информации, содержащейся в первом байте команды.

Командный цикл начинается с выборки команды. Первый машинный цикл М1 всегда цикл выборки команды (OF) из памяти, в нем МП считывает первый байт команды, содержащий код операции. После этого могут быть еще один или два МЦ типа MR, поскольку команда может быть однобайтной, двухбайтной или трехбайтной. Если команда трехбайтная, то она хранится в памяти так, как показано на рисунке 3.8, б.

После выборки и декодирования команды могут понадобиться дополнительные машинные циклы для ее выполнения. Всего в КЦ может быть от одного до пяти МЦ (М1…М5).

МЦ состоит из тактов, в которых выполняются типовые действия. Число тактов в различных МЦ – 3…6, но большинство МЦ содержит три такта. Такты – интервалы между одноименными фронтами тактовых импульсов.

Рассмотрим типовые действия МП, выполняемые в тактах различных машинных циклов.

Втакте Т1 происходят следующие процессы:

-адрес памяти или ВУ выставляется на шинах А15-8 и АD7-0;

-генерируется сигнал ALE для фиксации битов АD7-0 во внешнем регистре;

-на линиях IO/ M , S1 и S0 выставляется информация о типе МЦ;

-проверяется флаг HALT и при условии HALT = 0 МП переходит к такту Т2. В противном случае МП переходит в состояние «останов».

В такте Т2 выполняются следующие действия:

-проверяется вход READY, т. е. определяется готовность адресованного в такте Т1 устройства к обмену с МП;

-программный счетчик PC инкрементируется, если данный МЦ является частью выборки команды;

192

- во всех МЦ, кроме цикла BI (освобождения шин), один из управляющих

стробов |

RD |

, |

WR |

или |

INTA |

переходит в активное нулевое состояние. |

|

|

|

Такт ожидания TW появляется при неготовности памяти или ВУ к обмену с МП (READY = 0). Сигнал READY проверяется в каждом такте ожидания. Состояние линий адресов, данных и управления остаются теми же, что и в конце такта Т2. Такты ожидания вставляются до появления единичного сигнала READY, после чего МП переходит к такту Т3.

В такте Т3 байт команды или байт данных передается в МП или из него

положительным фронтом управляющего строба (RD, WR или INTA ). Управляющий строб возвращается в пассивное единичное состояние. Если данный МЦ является циклом M1, то за тактом Т3 следует такт Т4. В противном случае МЦ заканчивается.

В такте Т4 происходит декодирование принятой МП команды. Системные шины в этом такте не используются. Далее возможны два варианта – МЦ из четырех или из шести тактов.

Такты Т5 и Т6 вводятся при необходимости для завершения некоторых команд, в которых после их декодирования нужно произвести какие-либо внутренние действия. Системные шины не используются. Выполняются операции, внутренние для МП.

Затем проверяется флаг захвата шин HOLD, и если он установлен, то реализуется переход к режиму захвата на время существования сигнала HOLD, в течение которого осуществляется обмен данными между памятью и ВУ под управлением контроллера ПДП без участия МП.

При сброшенном флаге захвата шин определяется, является ли данный МЦ последним машинным циклом КЦ. Если этого нет, то начинается следующий МЦ с такта Т1. Если же данный МЦ завершает КЦ, то анализируется наличие или отсутствие запросов прерывания INT. Если такие запросы присутствуют, то

устанавливается активный уровень строба подтверждения прерывания INTA и сбрасывается триггер разрешения прерывания INTE (от англ. Interrupt Enable). После обработки запроса прерывания МП переходит к циклу М1 следующего КЦ.

Временные диаграммы цикла чтения с тактом ожидания приведены на рисунке 3.9.

В первом такте цикла чтения показаны сигналы, обеспечивающие формирование адреса ячейки памяти или ВУ. Во втором такте обнаруживается отсутствие готовности объекта к обмену с МП, приводящее к введению такта ожидания. В

193

такте ожидания появляется сигнал готовности, разрешающий переход к такту

Т3, в котором положительном фронтом строба чтения |

RD |

данные вводятся в МП. |

|

Интервалы действия тех или иных сигналов жестко определяются временными диаграммами МЦ. На рисунке 3.9 отмечены некоторые из этих интервалов:

-интервал tAD определяет максимальное время от момента выставления адреса до появления данных на шине AD7-0;

-интервал tAL отмечает момент загрузки младшего байта адреса во внешний регистр;

|

T1 |

T2 |

T |

T3 |

T1 (следующий МЦ) |

|

|

|

W |

|

|

|

CLK |

|

|

|

|

|

|

t |

|

|

|

|

|

AD |

|

|

|

A |

|

Cтарший полуадрес |

|

|

|

15-8 |

|

|

|

|

|

AD |

Младший |

|

|

Данные |

|

полуадрес |

|

|

|

||

7-0 |

|

|

|

|

|

tAL |

|

|

|

ввод |

|

|

|

|

данных |

|

|

ALE |

|

|

|

|

|

|

|

|

t RD |

tRA |

|

RD |

|

|

|

|

|

Ready |

|

|

|

|

|

|

t |

|

|

|

|

|

AC |

|

|

|

|

Рисунок 3.9 – Временные диаграммы цикла чтения МП

- интервал tAC отмечает время от момента выставления адреса до появления

активного уровня управляющего строба RD;

- интервал tRD задает длительность управляющего строба |

RD |

; |

|

- интервал tRA определяет время от момента чтения данных до появления нового значения адреса (за это время старые данные должны быть сняты с линии

AD7-0).

194

3.2.10 Блок управления прерываниями

При работе МПС в ней или вне ее могут произойти события, требующие немедленной реакции – прерывания выполняемой программы и перехода к обслуживанию возникшей ситуации. Внутри системы особые ситуации возникают при сбоях в работе, переполнении разрядной сетки, попытке деления на ноль и т. д. Ситуации подобного типа, связанные с ошибками в работе МП, называются ис-

ключениями.

Аппаратными прерываниями называют штатные ситуации, в которых прерывания запрашиваются внешними сигналами. Если же запрос формируется командами программы, то говорят о программных прерываниях. Аппаратные прерывания возникают также при требованиях обслуживания от ВУ. Извне могут поступать сигналы об аварийных ситуациях в управляемых объектах, неисправностях источников питания и др.

Аппаратные прерывания увеличивают производительность системы, позволяя ВУ занимать время МП только при их готовности к обмену. Когда ВУ нуждается в обслуживании, оно устанавливает триггер запроса прерывания, и сигнал запроса сохраняется, пока не будет воспринят и обработан МП. В ответ на при-

нятый запрос завершается выполнение текущей команды, запоминается в стеке состояние МП, выполняется подпрограмма обслуживания прерывания, восстанавливается состояние МП, и затем возвращается управление очередной команде основной программы.

При организации прерываний решаются задачи маскирования запросов и определяются их уровни приоритета при конфликтах из-за одновременного поступления нескольких запросов.

Маскирование состоит в запрещении действия соответствующего входа. Входы запросов прерывания могут быть маскируемыми или немаскируемыми, т. е. принимаемыми всегда. Маскируемые прерывания могут быть разрешены или запрещены командами EI (от англ. Enable Interrupt) и DI (от англ. Disable Interrupt), действующими на все маскируемые входы одновременно. Начальный сброс МП запрещает обслуживание маскируемых запросов, для их последующего разрешения следует ввести команду EI. Имеется также возможность раздельного маскирования запросов с помощью специальной команды SIM (от англ. Set Interrupt Mask).

Приоритеты входов вводятся для решения вопроса о том, какому запросу предоставить обслуживание при наличии одновременно нескольких. Простей-

195

Адреса ВУ могут размещаться в отдельном адресном пространстве (интер-

фейс с раздельной шиной) или же занимать часть общего (интерфейс с общей шиной).

В первом случае требуется наличие управляющих сигналов, определяющих,

с каким типом объектов ведется обмен. Например, вводится сигнал |

IO/ M |

, |

|

указывающий, адресуется память или ВУ. При этом память может использовать все АП. Для обмена с ВУ имеются только операции ввода IN port и вывода OUT port, и теряется возможность применять к данным от ВУ широкий набор команд, имеющихся для работы с данными, хранимыми в памяти.

Во втором случае обращение к ВУ происходит также, как и к ячейкам памяти, т. е. с помощью тех же команд и той же шины. Недостатком этой концепции интерфейса является сужение АП для памяти, поскольку часть АП занимается ВУ. Достоинство состоит в том, что над данными, получаемыми от ВУ, можно производить все те операции, которые имеются в системе команд МП для данных, находящихся в памяти.

Выбор адресованной ячейки памяти или ВУ осуществляется схемами декодирования адреса. При управлении памяти и ВУ МП должен вначале сформировать нужный адрес, который затем декодируется аппаратными средствами.

ВМПС применяют несколько способов формирования адресов или способов адресации. Для систем с простыми МП применяют прямую, прямую регистровую, косвенную и непосредственную адресации.

При прямой адресации адрес операнда содержится в команде, подлежащей выполнению. Прямая адресация удобна, но удлиняет команды, т. е. увеличивает их разрядности, так как при значительных емкостях памяти разрядности адресов достаточно велики.

Вслучае прямой регистровой адресации, операнд находится в одном из внутренних регистров МП, малоразрядный адрес которого указан в команде. В частности, для адресации восьми регистров общего назначения достаточны трехразрядные адреса, а для адресации четырех регистровых пар даже двухразрядные. В этом случае прямая адресация сочетается с компактностью команд и проявляет все свои достоинства.

При косвенной адресации в команде явно или неявно указывается регистр МП, содержащий адрес операнда, т. е. в команде указывается или подразумевается короткий адрес адреса. Команда компакта, но для ее выполнения требуется предварительная настройка – загрузка регистра косвенного адреса. Косвенная адресация особенно удобна при обработке списков, когда настройка произ-

199

водится однократно, а очередной адрес получается модификацией предыдущего (изменением его на еденицу).

При непосредственной адресации в команде содержится сам операнд. Использование различных способов адресации сокращает объем и время

выполнения программ.

Данные (исходные и результаты обработки) хранятся в памяти и МП в виде восьмиразрядных двоичных чисел, т. е. слово данных имеет формат один байт

(рисунок 3.12, а).

Команда может быть однобайтовой, двухбайтовой или трехбайтовой (ри-

сунок 3.12, б).

D |

7 |

D |

6 |

D |

5 |

D |

4 |

D |

3 |

D |

2 |

D |

1 |

D |

0 |

Байт данных |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

b |

1 |

|

|

– КОп + адресная часть |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Непосредственный операнд |

||||

КОп |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

или адрес ВУ |

|

|

|

b |

1 |

|

|

|

|

b |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Младший полуадрес |

|||

КОп |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

операнда |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

b |

1 |

|

|

|

|

b |

2 |

|

|

|

|

b |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Старший полуадрес |

|

|

|

|

|

|

б) |

|

|

|

|

|

|

|

|

операнда |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рисунок 3.12 – Форматы команд простого микропроцессора

Первый байт содержит код операции (КОп), сведения о способе адресации, а если команда однобайтовая, то и адрес операнда. Размещение адреса в однобайтовой команде возможно для операций типа «регистр-регистр» с короткими адресами.

Второй байт двухбайтной команды содержит непосредственный операнд либо адрес ВУ, а второй байт трехбайтной команды – младший полуадрес операнда или младший байт непосредственных данных при загрузке пары регистров.

Третий байт команды содержит старший полуадрес операнда или старший байт непосредственных данных при загрузке пары регистров.

200