- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

-

Рассмотрим основные блоки программируемого связного адаптера.

Буфер данных – это 8-разрядное двунаправленное устройство для обмена данными и управляющими словами между МС и ПСА через системную шину данных D(7-0).

Блок управления чтением и записью включает регистр режима, регистр команд и два регистра синхрослов которые, соответственно, служат: для хранения слова задания режима MI, для приёма команды CI, для хранения одного или двух слов синхронизации SYNC. Этот блок выполняет сравнение слов, хранящихся в регистрах синхрослов с содержимым регистров приемника, генерирует внутренние сигналы управления работой БИС.

Передатчик представляет собой 13-разрядный сдвиговый регистр, хранящий очередной выходной байт. Разряды 12 и 11 регистра используются для формирования стоп-битов, 10 - для записи контрольного бита, разряды 9-2 - для хранения данных, 1 - для формирования старт-бита, 0 - выходной буфер для последовательного вывода байта данных в линию TD (transmitter data) ПСА.

Блок управления передатчиком осуществляет прием новых байт данных из шины данных, при необходимости добавляет к ним контрольный бит, обрамляет стартовыми и стоповыми битами и синхронизирует вывод из сдвигового регистра передатчика.

Приемник представляет собой два 9-разрядных сдвиговых регистра. На эти регистры осуществляется последовательный ввод информации со входа RD (receiver data) ПСА.

Блок управления приемником формирует синхроимпульс приема, считает принятые биты, проводит контроль четности, устанавливает триггеры ошибок: ошибки четности PE (parity error), ошибки кода FE (framing error), ошибки переполнения OE (overrun error).

Блок управления модемом служит для формирования сигналов синхронизации обмена между МС и модемом или МС каким либо другим ПУ:

![]() (clear

to

send)

– готовность передатчика модема или

приемника ПУ принять данные с ПСА;

(clear

to

send)

– готовность передатчика модема или

приемника ПУ принять данные с ПСА;

![]() (request

to

send)

– запрос приемнику ПУ или передатчику

модема на прием данных из ПСА;

(request

to

send)

– запрос приемнику ПУ или передатчику

модема на прием данных из ПСА;

![]() (data

terminal

ready)

– запрос передатчику ПУ на передачу

данных в ПСА;

(data

terminal

ready)

– запрос передатчику ПУ на передачу

данных в ПСА;

![]() (data

set

ready)

– готовность ПУ передать данные в ПСА.

(data

set

ready)

– готовность ПУ передать данные в ПСА.

Назначение

управляющих сигналов

![]()

![]() ,

,

![]() ,

,

![]() может быть другим.

может быть другим.

11.2. Режимы работы связного адаптера

Передача и прием последовательной информации (символов) осуществляется соответственно на вывод TD или с вывода RD микросхемы адаптера путем передачи и приема битовых посылок. Одному байту данных, передаваемых из МС или в МС, соответствует последовательность битовых посылок, состоящая из последовательного кода данных и бита контроля (если последний запрограммирован).

Последовательные коды данных состоят из 5 – 8 бит и передаются (принимаются) начиная с младшего бита.

Бит контроля служит для контроля правильности принимаемых последовательных кодов данных. Этот бит формируется при передаче для каждого кода данных как сумма по модулю 2 всех битов кода данных. При приеме бит контроля для каждого кода данных определяется вновь и сравнивается с полученным битом контроля, после чего делается вывод о наличии или отсутствии ошибок при передаче данных.

ПСА может работать в двух режимах – синхронном и асинхронном.

Синхронный режим характеризуется непрерывным потоком передаваемой и принимаемой информации. Для установления синхронизации между ПСА абонентов, участвующих в обмене, и выделения из последовательного потока символов полезной информации в поток информации вводятся специальные кодирующие слова – синхросимволы, причем формат кода синхросимвола и кода данных выбирается одинаковым. Если между кодами данных имеются временные промежутки, то они заполняются синхросимволами. Синхросимволов может быть один или два (устанавливается программно). Если запрограммирован контроль кодов данных по четности (нечетности), то после каждого кода данных вставляется бит контроля.

Приём в синхронном режиме может выполняться с внешней и с внутренней синхронизацией.

При внутренней синхронизации приёмник ПСА не начинает приема кодов данных, пока не примет одно или два синхрослова.

При внешней синхронизации приемник ПСА начинает прием кодов данных только после поступления единичного синхроимпульса от ПУ на вход SYNDET/BD.

Частота

следования битов в последовательном

канале при синхронном режиме равна

частоте тактовых импульсов внешнего

генератора, подключенного ко входу

![]() для передатчика и ко входу

для передатчика и ко входу

![]() для приемника. Соотношение частот

для приемника. Соотношение частот

![]() и

и

![]() с системной частотой синхронизации

микросхемы fС,

поступающей на вход CLK:

с системной частотой синхронизации

микросхемы fС,

поступающей на вход CLK:

![]() .

Максимальная скорость передачи/приема

информации в синхронном режиме равна

64 Кбод.

.

Максимальная скорость передачи/приема

информации в синхронном режиме равна

64 Кбод.

Асинхронный режим характеризуется одиночными посылками информации, инициализация которых определяется либо МП системы, либо ПУ.

Обмен,

также как и при синхронном режиме

осуществляется последовательными

кодами данных с битами или без битов

контроля. Каждая одиночная последовательная

посылка, соответствующая коду данных

начинается со стартового

бита

-

сигнала низкого уровня,

длительность

которого равна длительности бита данных.

Стартовый бит служит для ввода в

синхронизацию передатчика/приемника

микросхемы адаптера. Завершается каждая

кодовая посылка стоповым

сигналом -

сигналом высокого уровня, длительностью

1 или 1,5 или 2 бита д анных.

Стоповый сигнал служит для определения

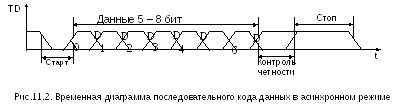

конца посылки. Временная диаграмма

последовательного кода данных в

асинхронном режиме приведена на рис.11.2.

анных.

Стоповый сигнал служит для определения

конца посылки. Временная диаграмма

последовательного кода данных в

асинхронном режиме приведена на рис.11.2.

Частота

битовых посылок в асинхронном режиме

задается равной либо 1, либо 1/16, либо

1/64 частоты внешнего синхрогенератора,

подключенного к выводу

![]() для передатчика и к выводу

для передатчика и к выводу

![]() для приемника адаптера. При этом должно

соблюдаться следующее соотношение

частот внешнего синхрогенератора

для приемника адаптера. При этом должно

соблюдаться следующее соотношение

частот внешнего синхрогенератора

![]() и

и

![]() с частой синхронизации микросхемы fC:

для частоты битовых посылок 1:1 -

с частой синхронизации микросхемы fC:

для частоты битовых посылок 1:1 -

![]() ;

для 1:16 и для 1:64 -

;

для 1:16 и для 1:64 -

![]() .

.

В настоящее время для обмена информацией между МС или компьютерами по последовательным каналам связи используется асинхронный режим обмена. Поэтому коммуникационные порты компьютеров (COM1 и COM2) выполняются на основе модифицированной микросхемы связного адаптера - i8250 – универсального асинхронного приемника/передатчика (UART) /38-40/.