- •Iпр.Макс – макс. Допустимый прямой постоянный ток

- •Идеализированная выходная характеристикя в активном режиме имеет вид:. Рабочий участок – прямая хар-ка. По вых. Хар-кам можно определить вых. Проводимость по пост. И перемен. Току.

- •Iвых.Макс – максимальный выходной ток

- •Условие работы бт в обл. Отс.

- •Преимущество синх-го rs-триггера:

Условие работы бт в обл. Отс.

В общем

случае Iк

в обл. отс. опр-ся обратным током

коллектора Iк.о. Iк.отс.

![]() Iк.о.

Iк.о.

![]()

Возможны три варианта запирания транзистора, которые определяют соотношения токов Iк.отс./ Iк.о.:

1) Пассивное запирание, когда Uвх. = 0, а цепь базы замкнута.

![]() ,

где

,

где

![]() =0,95

=0,95

![]() 0,995-

коэф-т передачи тока в схеме с ОБ.

0,995-

коэф-т передачи тока в схеме с ОБ.

![]() =0,6

=0,6![]() 0,8

– коэф-т передачи тока в схеме с ОБ в

инверсном вкл.

0,8

– коэф-т передачи тока в схеме с ОБ в

инверсном вкл.

Оценим соотношение Iк.отс./ Iк.о

Iк.отс.

![]() 5Iк.о.

5Iк.о.

Iк.о. существенно зависит от тем-ры (особенно для Ge)

Условие запирания транзистора ухудшается с ростом тем-ры.

2) Пассивное запирание Uвх=0,

цепь базы разомкнута. Iк.отс.

![]() Iк.о.

Iк.о.

Iк.отс.

![]() Iк.о.(

Iк.о.(

![]() +1)

+1)

![]() ,

при

,

при

![]() ,

Iк.отс.

,

Iк.отс.

![]() 4000Iк.о.

4000Iк.о.

Т.о. при этом варианте запирания Iк.отс становится соизмеримым с Iк.нас, т.е. транзистор не запирается. Большой Iк.отс. вызывает лавинообразный процесс саморазогрева, что может привести к выходу его из строя. Данный способ запирания явл-ся неблагоприятным и может исп-ся только для короткого измерения параметров БТ.

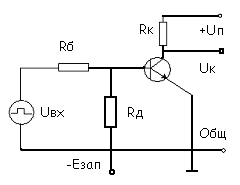

3) Активное запирание Uвх=0,

при котором на базу транзистора подается

оьратное запирающее переход БЭ напр.

Uвх.=-Eзап. Iк.отс.

![]() Iк.о.

Iк.о.

Данный способ обеспечивает наилучшее условие работы БТ в обл. отс.

Для реализации этого способа входной сигнал должен быть знакопеременным.

Такой сигнал можно получить с помощью импульсного трансформатора. Возможна также подача на базу постоянного обратного(отрицательного) напряжения от источника Eзап. ч/з данный резистор Rд.. при этом управляющий вх. Сигнал может быть однополярным.

Мощность рассеиваемая БТ в обл. отсечки

Pотс = Pк.отс

= Iк.отс.*Uк.отс

= Iк.отс(Uп-Iк.отс*Rк)

![]() Iк.отс.*Uп

Iк.отс.*Uп

№29. Импульсный режим работы БТ. Область переключения, время включения и выключения транзистора. Определение мощности, рассеиваемой транзистором при переключении.

При переключении транзистор некоторое время находится в активном режиме и может выделять в это время импульсную мощность, значительно большую, чем в обл. нас. И отсечки.

При открывании транзистора без форсировки

он ведет себя как мнерционное звено

1-го порядка с постоянной времени

![]()

![]()

![]() ,

где

,

где

![]() граничная частота усиления транзистора(это

нормируемый параметр).

граничная частота усиления транзистора(это

нормируемый параметр).

tвкл

tвкл![]() 3

3![]()

![]()

![]()

При форсировке включения транзистора закон построения тока Iк. близок к линейному:

tвкл =![]() ln(Кн/Кн-1)

ln(Кн/Кн-1)

, где Кн – коэффициент форсировки ![]()

При форсировке время вкл. транзистора уменьшится примерно в 6 раз. При выкл. транзистора в режиме активног запирания время выкл. опр-ся 2-мя состояниями:

-

tp- время рассасывания носителей в базе транзистора, занимающее основное время при выкл.

-

tз- время запирания

tвыкл = tр+ tз

Практически при определении tвыкл

берут tвыкл

![]() tр,

которое берется из справочника.

tр,

которое берется из справочника.

Мощность, рассеиваемая транзистором при переключении.

Pк.пер =Pн / 6*(tвкл+ tвыкл)/T Pн =Iк.нас*Uп

Pк.пер =Pн

/ 6*tпер*f f

увелич-ся

![]() Pк.пер

увел-ся

Pк.пер

увел-ся

При определении f транзистор может сгореть, т.е. может превысить допустимую мощность.

Мощность, рассеиваемая транзистором в обл. переключения нарастает пропорционально частоте входных импульсовf и при определенном значении этой частоты может привысить максимально допустимую Pк.макс(нормируемый параметр).

|

|

Диаграмма изменения мгновенной мощности, рассеиваемая на транзисторе в импульсном режиме. |

№30. Импульсный режим работы БТ. Характеристики импульсного сигнала. Схема импульсного каскада. Определение полной мощности, рассеиваемой транзистором, условие его выбора.

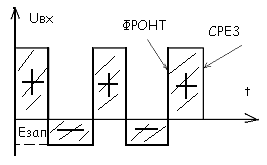

Параметры импульсного сигнала.

tи- длительность импульса

T-период следования импульса

f- частота следования импульсов

Кз=tи/T=0..1 – коэф-т заполнения (относительная длительность импульса)

Q=T/ tи =1..∞ -скважность импульсов.

Фронт импульса- перепад уровня от 0 до 1

Срез импульса – перепад уровня из 1 в 0

U1=Um – амплитуда импульса

Полная мощность рассеиваемая БТ в импульсном режиме:

Pк.и.=Кз*Pк.нас.+(1-Кз)*Pк.отс.+Рк.перек.

При условии (tвкл + tвыкл)<<T-период следования вх. импульсов

Кз- коэффициент заполнения. T=1/f

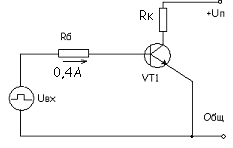

Выбор типа транзистора в импульсном режиме.

Условия выбора:

-

По напряжения Uк.макс>=(1,2-1,5)Uп – при выкл. Состоянии

-

По току Iк.макс>=(1,2-1,5)Uп/Rк=(1,2-1,5)Iк.нас. – при длительном вкл.

-

По мощности Pк.макс>=(1,2-1,5)Uк.нас.*Iк.нас.- для режима длительного вкл.

Pк.макс>=(1,2-1,5)Pк.имп. – при периодических импульсах.

4)Условие проверки по допустимому току базы Iб.нас, который не должен привышать выходной ток источника вх. сигнала (Iвых.1). Iб.нас<=Iвых.1

При невыполнении условия 4 выбирается

транзистор с большим значением

![]() или исп-ся составной транзистор.

или исп-ся составной транзистор.

№31. Логические элементы. Классификация. Элементы «И» и «ИЛИ» на ДРЛ-логике. Схемы, принцип действия, логическая функция, таблица состояний.

ЦУ по элементной базе разделяются:

1.ДРЛ – диодно-резисторная логика. В виде типовых устройств не выпускаются, а широко применяются в виде монтажного соединения диодов и резисторов на пультах управления и печатных платах.

2.РТЛ – резисторно-транзисторная логика К114, К115, К201(не выпускаются и не применяются)

3.ДТЛ – диодно-транзисторная логика. К120(не выпускаются и не применяются)

4.ТТЛ – транзисторно-транзисторная логика. К155, К555, К1533(отличительная особенность – высокое быстродействие, но сравнительно высокое потребление мощности). Находят самое широкое применение в системах автоматики и имеет наиболее развитый функциональный состав.

5.ЭСЛ эмиттерно-связная логика. К233. имеет ограниченное применение из-за большой потребляемой мощности. Отличается самым высоким быстродействием.

6.МОП – логика на МОП-транзисторах. К172. В настоящее время не выпускается имеет ограниченное применение из-за низкого быстродействия.

7.КМОП – логика на комплементарных МОП-транзисторах. К176, К564, К1564. Находит широкое применение. Отличаются очень малой потребляемой мощностью, но ограничены в быстродействии.

8.И2Л – инжекционно-интегральная логика. Перспективная элементная база. Серийного выпуска нет.

Логические элементы ДРЛ.

Могут выполнять только 2 логических операции: «И», «ИЛИ».

«ИЛИ»

1.Когда на всех входах ЛЭ присутствуют сигналы низкого уровня (логич. 0) диоды VD1..VDn закрыты м=и напряжение на выходе отсутствует(на выходе логич. 0).

U1 = U2 = U0 = 0

Uвых = U0вых = 0

2.если хотя бы на одном из входов ЛЭ присутствует сигнал высокого уровня(логич. 1), открывается соответствующий диод и часть входного напряжения поступает на выход. Получаем на выходе сигнал высокого уровня(логичю 1).

U1 = U1 U2 = U0 = 0

Uвых = U1вых = U1 – Uпр

Uпр = 0,6 – 0,7В(Si) – прямое падение напряжения на диоде

U1 = 2,4 – 12B

Диоды VD1..VDn исключают взаимную перегрузку источники сигнала, когда их уровни не одинаковы.

«И»

1.В отличие от предыдущей схемы ЛЭ ИЛИ в схеме ЛЭ «И» вводится внешний источник питания +Uп.

2.Диоды на входах ЛЭ включаются в прямом направлении отн. Источника питания +Uп.

3.Резистор RБ ограничивает выходной ток ЛЭ при логич. 0 на входах.

Если хотя бы на одном из входов ЛЭ присутствует сигнал низкого уровня, открывается соответствующий диод VD1, который шунтирует выходную цепь ЛЭ, при этом через этот диод протекает ток по цепи Uп – RБ – VD1 – U1 – общ.

U1 = U0 = 0 VD1 – открыт

Uвых = U0вых = Uпр = 0.65В

Если на всех входах ЛЭ присутствуют сигналы высокого уровня , все диоды VDn закрываются, напряжение питания Uп поступает через RБ на выход ЛЭ, получаем сигнал высокого уровня

U1 = U2 = U1 (VD1, VD2 закрыты)

Uвых = U1 = UП * RН / (RБ + RН), при RН >> RБ Uвых = UП

Недостатки ЛЭ ДРЛ: низкая нагрузочная способность(U1вых существенно снижается при подключении реальной нагрузки RH). Бесполезные потери мощности за счёт RБ I0вых = (UП - UПР) / RБ. невозможность реализации ЛЭ «НЕ», в связи с чем невозможно получить полный набор типовых ЛЭ.

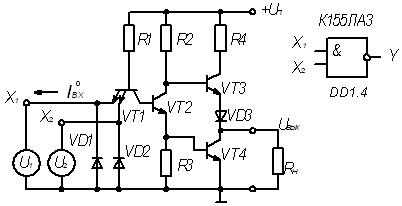

№32. Логические элементы ТТЛ. Базовый элемент «И-НЕ». Принцип действия. Входная и передаточная характеристики.

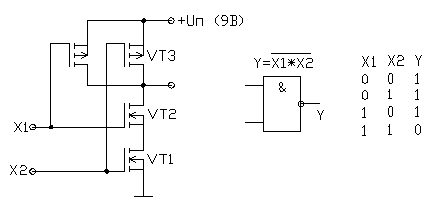

Базовым ЛЭ ТТЛ является элемент И-НЕ, на основе которого строятся другие типы ИС. Упрощенная схема базового ЛЭ 2И-НЕ серии К155 и его графическое обозначение приведены на рисунке 1.1.

Схема содержит 3 каскада, первый из которых выполнен на многоэмиттерном транзисторе VT1 и выполняет основную логическую операцию И. Диоды VDI и VD2 на входах ЛЭ защищают от пробоя эмиттерные переходы VT1 при отрицательных импульсах помехи на входе ЛЭ. Резистор R1 ограничивает ток базы VT1.

Второй каскад на транзисторе VT2 является фазорасщепителем и формирует на своих двух выходах сигналы противоположных уровней.

Третий каскад - двухтактный усилитель мощности на транзисторах VT3 и VT4. Служит для повышения нагрузочной способности ЛЭ. Резистор R4 защищает выход ЛЭ при коротких замыканиях нагрузки и ограничивает сквозной ток через транзисторы VT3 и VT4 при их переключении. Диод VD3 обеспечивает надежное запирание VT3.

|

X1 |

X2 |

Y |

|

0 0 1 1 |

0 1 0 1 |

1 1 1 0 |

Рисунок 1.1

Схема работает следующим образом. Если хотя бы на один из входов ЛЭ подан сигнал низкого уровня (логический нуль), например, U0вх.1 < 0,4В, то за счет прямого напряжения Uп источника питания (ИП) открывается соответствующий переход база-эмиттер (Б-Э) VT1 и через него протекает во входную цепь сравнительно большой ток, ограниченный резистором R1:

![]()

При этом транзисторы VT2 и VT4 оказываются закрытыми, так как низкого потенциала базы VT1 (Uб=1,1В) недостаточно для отпирания трех переходов: коллекторного VT1 и двух эмиттерных VT2 и VT4. Высокий потенциал на коллекторе закрытого VT2 обеспечивает отпирание VT3, который переходит в режим насыщения. Открытый транзистор VT3 подключает выход ЛЭ через R4 и VD3 к шине питания Uп, и на выходе ЛЭ получаем сигнал высокого уровня (логическую единицу):

![]()

Без нагрузки Rн падением напряжения на резисторе R4 можно пренебречь, так как протекающий через него ток отсечки VT4 мал. При подключении Rн это падение увеличивается и U1вых уменьшается. Если на все входы ЛЭ поданы сигналы высокого уровня U1вx > 2,4В, то переходы Б-Э транзистора VT1 закрываются, входной ток уменьшается и меняет направление. Его значение определяется обратным током р-n перехода (I1вх = Iобp < 40мкА). В этом случае переход Б-К VT1 открывается и через него от ИП протекает в базу VТ2 ток, ограниченный сопротивлением R1. VT2 открывается и открывает VT4, который входит в режим насыщения и подключает выход ЛЭ к общей шине. Кроме того этот выход отключается от ИП, так как VT3 закрывается низким потенциалом коллектора открытого VT2. Выходной сигнал уменьшается до уровня логического нуля, который определяется напряжением насыщения коллекторного перехода VT4 (U0вых = Uк.нас. < 0,3В). Таким образом, схема выполняет логическую операцию И-НЕ в соответствии с таблицей состояний 1.2.

Передаточная характеристика представляет собой зависимость Uвых = f(Uвx). Для ЛЭ И-НЕ эта зависимость обратна и нелинейна, а ее график имеет три основных участка (рисунок 1.2,а). На первом участке (точки 1-2) открыт выходной транзистор VT3 и закрыт VT4, выходное напряжение максимально (Uвых = U1вых). На третьем участке (точки 6-7) транзистор VT3 закрыт, а VT4 открыт и выходное напряжение минимально (Uвых = U0вых). На втором наклонном участке (точки 3-4-5) транзисторы VT3, VT4 переключаются и через них может проходить, достаточно большой сквозной ток от ИП. В этом режиме ЛЭ должен работать минимальное время, так как на транзисторах VT3 и VT4 выделяется максимальная мощность.

Входная характеристика выражает зависимость Iвх = f(Uвх). Эта зависимость также обратна и нелинейна (рисунок 1.2,б). При логическом нуле на входе ток Iвх максимальный по величине и вытекающий из ЛЭ по направлению. Это ток ИП, проходящий через открытый переход Б-Э VT1. Если на вход ЛЭ подан сигнал высокого уровня, переход Б-Э закрыт, входной ток Iвх имеет минимальную величину, создается источником сигнала и является втекающим по направлению.

№33. Логические элементы ТТЛ. Основные достоинства и недостатки, условия согласования с источником сигнала и нагрузкой.

Преимущества ИС ТТЛ:

1.Высокое быстродействие

2.Высокая нагрузочная способность

I1вых макс = 10 мА(ТТЛ)

I1вых макс = 1,2 мА(КМОП)

3.Возможность «висячей единицы» на выходах ЛЭ, что упрощает схемотехнику цифровых утройств

4.большая надёжность из-за меньшего влияния Эл.-магн. Помех и статического электричества.

Условия согласования.

Эти условия нормируют уровни напряжений логического нуля (0< U0вx < 0,4В) и логической единицы (2,4В < U1вх < 5В), а также сопротивление источника сигнала Rист. Сопротивление Rист не должно превышать определенной величины при логическом нуле на входе, чтобы исключить образование ложной единицы за счет падения напряжения на Rист от вытекающего тока I0вх:

![]() .

.

При U1вх сопротивление Rист может быть любым (0 < R1ист < ), так как переход Б-Э VT1 закрыт, а переход Б-К открыт и его состояние не зависит от сопротивления входной цепи. Обрыв входной цепи ЛЭ ("висячая" единица) дает такой же результат, как действие потенциальной единицы. Поэтому ЛЭ ТТЛ может управляться контактом выключателя без источника входного сигнала (R0ист=0; R1ист=).

№34. Логические элементы на КМОП-транзисторах. Основные параметры, достоинства и недостатки. Элемент «НЕ», схема, принцип действия.

Параметры этих элементов близки к идеальным, кроме быстродействия.

Схема ЛЭ содержит комплементарные пары полевых транзисторов с каналом р-типа и n-типа. Топология этих элементов допускает высокую плотность упаковки элементов в кристалле, что позволяет создавать БИС(4-5ст. интеграции). К176 – базовая, К561, К564 – более совершенны, К1564 – наилучшие показатели(совместима с ТТЛ).

1.Если на вход ЛЭ подан сигнал низкого уровня (логич 0). VT1 закрыт, т.к. Uзи1<Uпор VT2 открыт.Uзи2 = Uвх – Uп = 0 – Uп = -9В |-Uзи2| > |Uпор|. Получаем на выходе сигнал высокого уровня. Uвых = U1 = Uп.

2.если на вход ЛЭ подан сигнал высокого уровня U1 = Uп, то VT1 открывается т.к. Uзи1 = Uвх > Uпор, а VT2 закрывается т.к. на его затворе отн. Его истока образуется низкий потенциал. Uзи2 = Uвх – Uп = 9-9=0

Т.о. выход ЛЭ отключается от шины питания и подключается к общему проводу. Получаем на выходе сигнал низкого уровня. Uвых = U0 = Uс.нас = 0,1В.

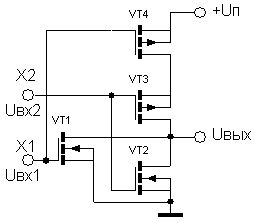

№35. Логический элемент «И-НЕ» на КМОП-транзисторах. Схема, принцип действия.

Нижние транзисторы VT1 , VT2 выполняют основную логич.операцию «И», поэтому они соединены последовательно. VT4 выполняет функцию внутренней нагрузки при VT1, VT2, а также обеспечивает инвертирование выходного стгнала.

-

Если хотя бы на одном из входов ЛЭ подан сигнал низкого уровня(логич 0), закрывается соответствующий нижний транзистор(VT1), но открывается соответствующий верхний транзистор VT3, т.о. выход ЛЭ отключается от общего провода и подключается к шине питания. Получаем на выходе сигнал высокого уровня. Uвх = U0 = 0 Uвх2 = U1 VT1 закрыт VT3 открыт На выходе : Uвых = U1 = Uп

-

Если на все выходы ЛЭ поданы сигналы высокого уровня, открываются все верхние транзисторы. Выход ЛЭ отключается от шины питания и подключается к общему проводу. Получаем на выходе 0

Uвх1=Uвх2=U1

VT1, VT2 – открыты VT3, VT4 – закрыты

Uвых = U0 = 0,1B

№36. Логический элемент «ИЛИ-НЕ» на КМОП-транзисторах. Схема, принцип действия.

![]()

|

x2 |

x1 |

y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Логич. операцию “или” выполняют два параллельно соедин. транзистора VT1, VT2.

VT3, VT4 обеспечивают инвертирование вых. сигнала.

1) при 2-х нулях на входе VT1, VT2 закрыты, а VT3, VT4 открыты. На выходе логич. “1”

2) При наличии хотя бы одной единицы на входе в соответствующий транзистор VT1 или VT2 открываются, а верхний (соотв-щий) закрывается (VT3, VT4).

Выход ЛЭ отключается от Uп и подключ. к общему проводу через открытый транзистор, получаем на выходе логич. “0”

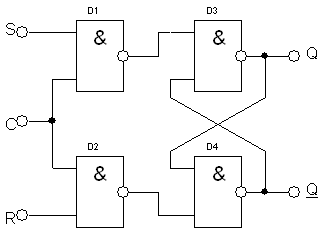

№37. Триггеры. Основные типы, применение. Структура асинхронных и синхронных RS-тригеров. Принцип действия, таблица состояний.

В последовательностных устройствах выходной сигнал определяется не только поданными на вход сигналами, но и предыдущим состоянием выходов. То есть эти устройства обладают памятью. К последовательностным устройствам относятся триггеры, регистры памяти и регистры сдвига, различные счетчики импульсов.

Простейшим устройством памяти явл-ся триггер.

Таблица

3.1

R

S

0

1

1

0

0

0

1

0

1

0

0

1

0

0

0

1

1

1

0

0

![]()

![]()

Разновидность триггеров:

1) RS-триггер асинхронный (2 входа)

2) RS-триггер синхронный (3 входа)

3) T-триггер (счетный) (1 вход)

4) D-триггер синхронный, универсальный (4 входа)

5) JK-триггер синхронный, универсальный (5 входов)

Рисунок

3.1

Схема RS-триггера (рисунок

3.1) содержит два логических

элемента (ЛЭ) D1 и D2,

охваченных перекрестными цепями

положительной обратной связи (ПОС).

Состояние триггера оценивается по

сигналу на прямом выходе

![]() .

На другом (инверсном) выходе

.

На другом (инверсном) выходе

![]() ,

сигнал должен иметь противоположный

уровень. Для установки триггера в

единичное состояние (

,

сигнал должен иметь противоположный

уровень. Для установки триггера в

единичное состояние (![]() )

предназначен вход S, а в

нулевое (

)

предназначен вход S, а в

нулевое (![]() )

- вход R. Работа триггера

обуславливается таблицей состояний

ЛЭ ИЛИ-НЕ. Единичное состояние триггера

(

)

- вход R. Работа триггера

обуславливается таблицей состояний

ЛЭ ИЛИ-НЕ. Единичное состояние триггера

(![]() )

получим при нулевых сигналах на обоих

входах ЛЭ D1 (

)

получим при нулевых сигналах на обоих

входах ЛЭ D1 (![]() ),

для чего надо подать единичный сигнал

S=1 на нижний вход ЛЭ

D2. Это состояние затем сохранится

и после прекращения единичного сигнала

на входе S, так как такой

сигнал будет подаваться на верхний

вход D2 с выхода

),

для чего надо подать единичный сигнал

S=1 на нижний вход ЛЭ

D2. Это состояние затем сохранится

и после прекращения единичного сигнала

на входе S, так как такой

сигнал будет подаваться на верхний

вход D2 с выхода

![]() .

.

Для переключения триггера в нулевое

состояние (![]() )

необходимо подать на вход

R сигнал 1, а на входе

S сохранить 0. Процесс

переключения триггера имеет лавинообразный

характер за счет действия ПОС, поэтому

время переключения очень мало.

)

необходимо подать на вход

R сигнал 1, а на входе

S сохранить 0. Процесс

переключения триггера имеет лавинообразный

характер за счет действия ПОС, поэтому

время переключения очень мало.

При сигналах R=S=0

выходной сигнал Q может

быть единичным или нулевым в зависимости

от предыдущего сочетания входных

сигналов R и

S (таблица 3.1). При

подаче сигналов R=S=1

триггер утрачивает свои типичные

свойства, так как на обоих выходах

устанавливается сигнал одного уровня

![]() .

Поэтому такой режим работы допускать

нельзя. Если обозначить состояние

триггера после подачи входных сигналов

буквами

.

Поэтому такой режим работы допускать

нельзя. Если обозначить состояние

триггера после подачи входных сигналов

буквами

![]() ,

а до подачи -

,

а до подачи -

![]() ,

то таблицу состояний можно упростить

(таблица 3.2).

,

то таблицу состояний можно упростить

(таблица 3.2).

Таблица

3.2

R

S

Режим

0

0

Хранение

0

1

1 0

Запись 1

1

0

0 1

Запись 0

1

1

Х X

Запрещено

![]()

![]()

![]()

![]()

1.2) RS-триггер на ЛЭ И-НЕ

Структура этого триггера (рисунок 3.2,а) аналогична предыдущей, но в отличие от рассмотренной схемы активным уровнем сигнала, переключающим данный триггер, является не единичный, а нулевой, что объясняется свойствами ЛЭ И-НЕ. Поэтому, в таблице состояний (таблица 3.3) все режимы работы противоположны рассмотренным, а в обозначении (рисунок 3.2,б) введен знак инверсии на входах R и S.

Таблица

3.3

R

S

Режим

0

0

x

Запрещено

0

1

1

Запись 0

1

0

0

Запись 1

1

1

Хранение

Рисунок

3.2

![]()

![]()

2) RS-триггер синхронный (тактируемый)

В отличие от рассмотренных простейших RS- триг. синхронный триггер, кроме R и S входов, имеет отдельный вход C, сигнал на котором обеспечивает переключение триггера в новое состояние.

Триггер меняет свое состояние в момент передачи синхроимпульса на вход C, а новое состояние триггера задается сигналами на входах R, S.

При C=0 обеспечивается режим хранения.

C=1 {запись 1 при S=1, R=0} {запись 0 при S=0, R=1} C=S=R=1 – запрет

Отсутствие инверсии записываемых сигналов по входу S объясняется двойной инверсией сигналов вх-й цепи.