704_Mikushin_A.V._Skhemotekhnika_mobil'nykh_radiostantsij_

.pdfиспользованы одноразрядные двоичные числа A и B; сумма – это одноразрядное двоичное число S; перенос обозначен буквой P; для обозначения входа переноса используется сочетание букв PI (I – сокращение от английского слова input, вход); для обозначения выхода переноса используется сочетание букв PO (O – сокращение от английского слова output, выход).

Таблица 3.1. Таблица истинности полного двоичного одноразрядного сумматора

|

|

|

|

|

|

Математическое |

|

№ |

PI |

A |

B |

S |

PO |

выражение |

|

|

|

||||||

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0+0+0=010 (002) |

|

2 |

0 |

0 |

1 |

1 |

0 |

0+0+1=110 (012) |

|

3 |

0 |

1 |

0 |

1 |

0 |

0+1+0=110 (012) |

|

4 |

0 |

1 |

1 |

0 |

1 |

0+1+1=210 (102) |

|

5 |

1 |

0 |

0 |

1 |

0 |

1+0+0=110 |

(012) |

6 |

1 |

0 |

1 |

0 |

1 |

1+0+1=210 |

(102) |

7 |

1 |

1 |

0 |

0 |

1 |

1+1+0=210 |

(102) |

8 |

1 |

1 |

1 |

1 |

1 |

1+1+1=310 |

(112) |

|

|

|

|

|

|

|

|

Схема, соответствующая таблице истинности, содержащейся в таблице 3.1, приведена на рисунке 3.1. Она построена по правилам разработки цифровых логических схем СДНФ (совершенная дизъюнктивная нормальная форма). Для ее реализации выбираются строки, в которых в выходном сигнале содержится единица. Для каждого выходного сигнала строится независимая схема. Для выхода S требуются строки 2, 3, 5 и 8. Для реализации каждой строки потребуется трехвходовый логический элемент 3И. На его входы будут подаваться прямые сигналы там, где в таблице содержится единица и инверсные там где содержится логический ноль.

Например, для строки 2 без инверсии следует подать сигнал B, а сигналы A и PI проинвертировать. Для строки 8 ни один из входных сигналов инвертировать не нужно. Аналогичным образом реализуется и схема для выхода PI.

211

Рисунок 3.1. Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора

Схему полного одноразрядного сумматора можно минимизировать. Для этого достаточно посмотреть на две последние строки его таблицы истинности. Мы можем увидеть, что сигнал переноса в них не зависит от сигнала, присутствующего на входе B. Поэтому этот вход можно не заводить на вход схемы “И”. В результате вместо двух нижних элементов “3И” можно воспользоваться одним двухвходовым элементом “2И”. Точно такая же ситуация возникает если рассмотреть строки 6 и 8. Здесь лишним оказывается вход A. Вход PI оказывается лишним в выражениях, описывающих строки 4 и 8. В результате схема формирования переноса упрощается и приобретает вид, приведённый на рисунке 3.2.

212

Рисунок 3.2. Минимизированная принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора

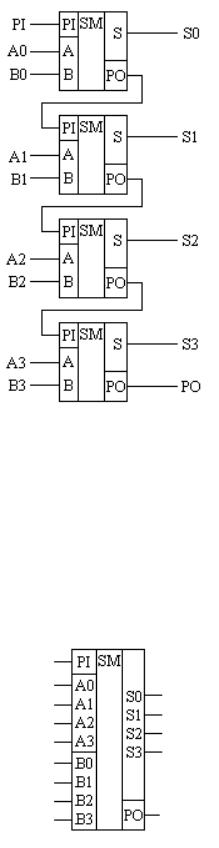

Примером одноразрядного двоичного сумматора может служить микросхема К155ИМ1. Условно-графическое обозначение полного двоичного одноразрядного сумматора показано на рисунке 3.3.

Рисунок 3.3. Изображение полного двоичного одноразрядного сумматора на схемах

Для того чтобы получить многоразрядный сумматор, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Схема реализации четырехразрядного сумматора на основе четырех одноразрядных приведена на рисунке 3.4.

213

Рисунок 3.4. Принципиальная схема многоразрядного двоичного сумматора

Полный двоичный четырехразрядный сумматор изображается на схемах с использованием условно-графического обозначения, показанного на рисунке 8. Обратите внимание, что в этом обозначении входы двоичного слова A объединены в отдельное поле. Точно так же объединены входы двоичного слова B. Вход и выход сигналов переноса на этом обозначении выделены в отдельные поля тоже. Изображённая таким образом микросхема намного более наглядно отображает свои функции.

Рисунок 3.5. Условно-графическое обозначение полного двоичного 4-разрядного сумматора на схемах

Приведенная на рисунке 3.5 схема двоичного сумматора не оптимизирована по быстродействию, она служит лишь для пояснения принципа действия

214

многоразрядного двоичного сумматора. В применяемых на практике схемах никогда не допускают последовательного распространения переноса через все разряды многоразрядного сумматора, так как это снижает его быстродействие. Для увеличения скорости работы двоичного сумматора используется отдельная схема формирования переносов для каждого двоичного разряда. Таблицу истинности для такой схемы легко получить из алгоритма суммирования двоичных чисел, а затем применить хорошо известные нам принципы построения цифрового устройства по произвольной таблице истинности.

Следующим широко используемым в схемах цифровой обработки сигналов устройством является цифровой двоичный умножитель. Эти устройства используются как в схемах масштабирования или гетеродинов, так и в составе цифровых фильтров.

Цифровые умножители

Умножение в двоичном виде производится подобно умножению в десятичной системе счисления. Как мы это помним из школьного курса, легче всего осуществлять умножение в столбик. При реализации этого алгоритма потребуется перемножить каждый разряд множимого на соответствующий разряд множителя.

Рассмотрим в качестве примера умножение двух четырёхразрядных двоичных чисел. Пусть требуется умножить число 10112 (1110) на число 11012 (1310). В результате умножения мы ожидаем получить число 100011112 (14310). Выполним операцию умножения в столбик в двоичной системе, как это показано на рисунке 3.6.

11011011

1101

1101

11010000

10001111

Рисунок 3.6. Алгоритм операции умножения в столбик

Для формирования произведения требуется вычислить четыре частичных произведения. Обратите внимание, что в двоичной арифметике требуется выполнять умножение только на числа 0 и 1. Это означает, что нужно либо суммировать множимое к сумме остальных частичных произведений, либо нет. Таким образом, для формирования частичного произведения можно воспользоваться логическими элементами “2И”.

Для формирования частичного произведения, кроме операции умножения на один разряд, требуется осуществлять его сдвиг влево на число разрядов, со-

215

ответствующее весу разряда множителя. Сдвиг можно осуществить простым соединением соответствующих разрядов частичных произведений к необходимым разрядам двоичного сумматора.

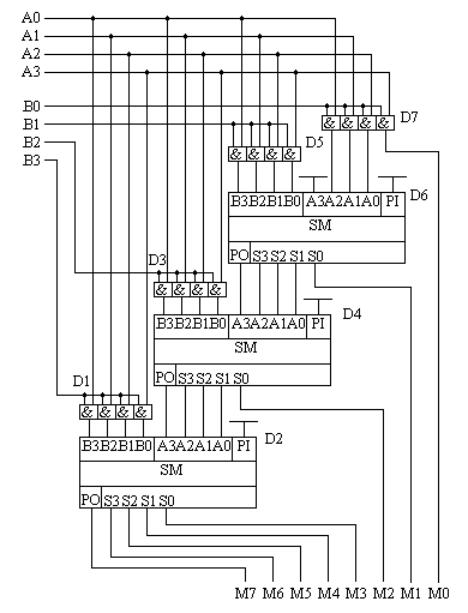

Для того чтобы принципиальная схема умножителя была похожа на алгоритм двоичного умножения, приведённый на рисунке 3.6, используем условнографические изображения микросхем, где входы расположены сверху, а выходы снизу. В полном соответствии с алгоритмом умножения в столбик нам потребуются три четырёхразрядных сумматора.

Принципиальная схема умножителя, реализующая алгоритм двоичного умножения в столбик, приведена на рисунке 3.7. Формирование частичных произведений в этой схеме осуществляют микросхемы D1, D3, D5, D7. В этих микросхемах содержится сразу четыре логических элемента “2И”.

Рисунок 3.7. Схема матричного умножителя 4 4

216

Сумматор, выполненный на микросхеме D6, суммирует первое и второе частные произведения. При этом младший разряд первого частного произведения не нуждается в суммировании (см. рисунок 3.6). Поэтому он подаётся на выход умножителя непосредственно (разряд M0).

Второе частное произведение должно быть сдвинуто на один разряд. Это осуществляется тем, что младший разряд выходного числа сумматора D6 соединяется со вторым разрядом произведения (M1). Но тогда первое частное произведение необходимо сдвинуть на один разряд влево по отношению ко второму частному произведению! Это выполняется тем, что младший разряд группы входов A соединяется с первым разрядом частного произведения, первый разряд группы входов A соединяется со вторым разрядом частного произведения, и т.д. Однако старший разряд группы входов A не с чем соединять! Вспомним, что если записать слева от числа ноль, то значение числа не изменится, поэтому мы должны этот разряд соединить с общим проводом схемы, добавляя тем самым ноль в старший разряд первого частного произведения.

Точно таким же образом осуществляется суммирование третьего и четвёртого частного произведения. Это суммирование выполняют микросхемы D4 и D2 соответственно. Отличие заключается только в том, что здесь не нужно задумываться о старшем разряде предыдущей суммы, ведь предыдущая микросхема сумматора формирует сигнал переноса.

Если внимательно посмотреть на схему умножителя, приведенную на рисунке 3.7, то можно увидеть, что она образует матрицу, сформированную проводниками, по которым передаются разряды числа A и числа B. В точках пересечения этих проводников находятся логические элементы “2И”. Именно по этой причине умножители, реализованные по данной схеме, получили название матричных умножителей.

Скорость работы схемы, приведенной на рисунке 3.7, определяется максимальным временем распространения сигнала. Это цепь D7, D6, D4, D2. Время работы схемы можно сократить, если сумматоры располагать не последовательно друг за другом, как это предполагается алгоритмом, приведенным на рисунке 3.6, а суммировать частичные произведения попарно, затем суммировать пары частичных произведений и т.д. В этом случае время выполнения операции умножения значительно сократится.

Особенно заметен выигрыш в быстродействии при построении многоразрядных умножителей, однако ничего не бывает бесплатно. В обмен на быстродействие придётся заплатить увеличением разрядности сумматоров, а значит сложностью схемы. Если сумматоры частных произведений останутся той же разрядности, что и ранее, то разрядность сумматоров пар частичных произведений должна быть увеличена на единицу. Разрядность сумматоров четвёрок частичных произведений будет на два разряда больше разрядности сумматоров частичных произведений, так как при суммировании четырёх чисел их значение в наиболее неблагоприятном случае может увеличиться в четыре раза, и т.д.

Умножители широко применяются в схемах обработки сигналов для изменения коэффициента передачи устройства, для реализации преобразователей частоты, и как составляющая часть цифровых фильтров.

217

Теперь рассмотрим следующий блок, часто используемый в схемах формирования цифровой обработки и сигналов. Это постоянные запоминающие устройства.

Постоянные запоминающие устройства

При выборе формы сигналов очень важно, чтобы этот сигнал не искажался при передаче по линиям связи. В цифровых устройствах не искажаются прямоугольные сигналы. Однако как только мы попытаемся передать их через аналоговые цепи, такие как усилители мощности, фильтры или антенны, прямоугольные сигналы будут искажены.

Для передачи по аналоговым цепям идеально подходят синусоидальные сигналы. Именно они не искажаются при распространении по таким цепям. У этих сигналов может измениться только амплитуда и фаза. Поэтому для работы в системах мобильной радиосвязи мы должны уметь генерировать сигналы такой формы.

Самый простой способ получить синусоидальную функцию – это считать её из таблицы. А это в свою очередь означает, что эту таблицу где-то надо хранить. Нам нужно запоминающее устройство. Причём такое устройство, которое может хранить информацию и при выключенном питании. Такое устройство получило название постоянное запоминающее устройство – ПЗУ.

Масочное ПЗУ

В цифровых устройствах удобнее всего хранить информацию в двоичном коде. Но ведь в этом случае можно просто соединять соответствующий бит слова с шиной питания или общим проводом. При формировании сигнала отсчёты амплитуды сигнала нам будут требоваться последовательно, то есть все данные не требуется одновременно, поэтому простейшие устройства для запоминания постоянной информации можно построить на мультиплексорах. Схема такого постоянного запоминающего устройства приведена на рисунке 3.8.

Рисунок 3.8. Схема простейшего постоянного запоминающего устройства, реализованная на мультиплексоре

218

В этой схеме построено постоянное запоминающее устройство на восемь одноразрядных ячеек. Запоминание конкретного значения бита в ячейку этого ПЗУ производится присоединением входа мультиплексора к источнику питания (запись единицы) или подключением к общему проводу (запись нуля). Выбор конкретной ячейки памяти осуществляется при помощи адресных входов A0 … A2. В приведённой на рисунке 3.8 схеме это входы управления мультиплексора.

Постоянные запоминающие устройства это универсальные схемы. Во многих устройствах информация на выходе ПЗУ не требуется постоянно. Она должна быть предоставлена только по специальному запросу. Этот запрос формирует сигнал RD. Название этого сигнала расшифровывается как read (чтение). Сигнал чтения тоже можно завести на внутренний дешифратор мультиплексора, как это показано на рисунке 3.8. При этом содержимое ячейки памяти появится на выходе ПЗУ только при активном сигнале чтения RD. При всех других условиях выход микросхемы будет оставаться в высокоомном состоянии.

Обычно при создании устройств памяти решается ещё одна задача – это возможность увеличения объёма памяти. Расширить объем памяти можно с помощью дополнительного дешифратора адреса. Но его нужно каким-либо способом подключать к микросхемам памяти для того, чтобы запрещать или разрешать работу выбираемых микросхем.

Для подключения дополнительного дешифратора адреса в микросхеме ПЗУ служит ещё один вход – CS (chip select – выбор кристалла). У постоянного запоминающего устройства эта функция совпадает с функцией чтения содержимого памяти, поэтому сигнал выбора кристалла CS и сигнал чтения RD можно объединить при помощи логического элемента “2И”.

На принципиальных схемах цифровых устройств микросхемы запоминания постоянной информации (ПЗУ) обозначаются, как показано на рисунке 3.9. На этом рисунке приведено обозначение, соответствующее схеме, показанной на рисунке 3.8. Надпись ROM в среднем поле обозначения микросхемы является сокращением от английских слов read only memory (память доступная только для чтения).

Рисунок 3.9. Обозначение постоянного запоминающего устройства на принципиальных схемах

Для целей цифровой обработки сигналов при хранении отсчётов амплитуды сигнала недостаточно одного двоичного разряда. Обычно для запоминания

219

конкретного значения напряжения используются многоразрядные двоичные числа.

Для того чтобы увеличить разрядность ячейки памяти ПЗУ микросхемы можно соединять параллельно. При этом информационные выходы и записанная в одноразрядных ячейках информация естественно остаются независимыми. Схема параллельного соединения одноразрядных ПЗУ для реализации многоразрядного ПЗУ приведена на рисунке 3.10, а условно-графическое обозначение микросхемы многоразрядного ПЗУ на принципиальных схемах на рисунке

3.11.

Как видно из приведённой на рисунке 3.10 схемы, адресные входы ПЗУ объединяются параллельно. При этом возрастает общий входной ток по каждому из адресных входов. Для того чтобы этого не происходило, на адресных входах можно применить усилители сигнала. В качестве усилителей цифрового сигнала, можно использовать самые обыкновенные инверторы, как это показано на рисунке 3.10. С точно такой же целью поставлены инверторы и на входах чтения и выбора кристалла.

Рисунок 3.10. Схема многоразрядного ПЗУ

220