- •36. Физический интерфейс 8048 и расширение ресурсов

- •38. Расширение памяти программ микропроцессора к1816ве48.

- •39. Расширение памяти данных микропроцессора к1816ве48.

- •37. Расширение пространства ввода- вывода программ микропроцессора к1816ве48.

- •40. Расширение числа прерываний методом поллинга

- •41. Система команд микропроцессора к1816ве48. Команды пересылки с регистровым способом адресации

- •42. Система команд микропроцессора к1816ве48. Команды пересылки с косвенно-регистровым способом адресации

- •60. Подключение исполнительных устройств к портам микропроцессора к1816ве48.

36. Физический интерфейс 8048 и расширение ресурсов

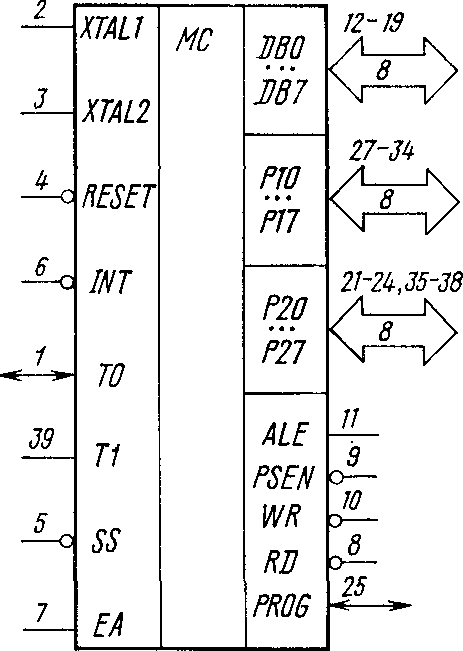

Условное графическое обозначение 8048 приведено на рис.1. Приборы размещаются в стандартных 40-выводных корпусах типа 2123.40 с двухряд- ным расположением выводов.

Рисунок 1 – УГО 8048

Состав физического интерфейса 8048:

Обозначение |

Номер вывода |

Описание |

VSS |

20 |

Общий |

VDD |

26 |

Напряжение питания +5 В или +21 В в режиме программирования УСППЗУ |

VCC |

40 |

Напряжение питания +5 В |

PROG |

25 |

Выходной строб для расширителя ВВ или про- граммирующий импульс +18 В в режиме про- граммирования УСППЗУ |

P1.0 – P1.7 |

27 – 34 |

Псевдодвунаправленный 8-разрядный порт ВВ |

P2.0 – P2.7 |

|

Псевдодвунаправленный 8-разрядный порт ВВ, младшая тетрада которого Р2.0 – Р2.3 использу- ется для вывода старшей части адреса при обра- щении к внешней памяти программ или как ка- нал связи с расширителем ВВ |

DB0 – DB7 |

12 – 19 |

Двунаправленный 8-разрядный канал ВВ данных либо синхронно со стробами RD, WR, либо асин- |

|

|

хронно. При обращении к внешней памяти про- грамм используется для выдачи младшего байта адреса синхронно с ALE и приема очередного байта программной последовательности син- хронно с PSEN. При обращении к внешней па- мяти данных служит для выдачи младшего байта адреса памяти синхронно с ALE и передачи дан- ных в соответствии со стробами RD, WR |

ALE |

11 |

Строб приема адреса. Генерируется в начале каж- дого машинного цикла и может быть применен для синхронизации внешних цепей |

RD |

8 |

Строб чтения данных. Генерируется в циклах чтения шины BUS. Используется как строб чте- ния внешней памяти данных |

WR |

10 |

Строб выдачи данных. Генерируется в циклах вывода информации через шину BUS. Применя- ется как строб записи данных во внешнюю па- мять |

RESET |

4 |

Вход начальной установки. Используется в режи- мах программирования УСППЗУ |

PSEN |

9 |

Строб чтения внешней памяти программ |

EA |

7 |

Разрешение доступа к внешней памяти. Применя- ется для запрета внутреннего ПЗУ в режимах эмуляции и отладки. Подача на вход напряжения +18 В переводит прибор в режим программиро- вания УСППЗУ |

SS |

5 |

Пошаговый режим. Используется совместно с ALE для организации пошагового исполнения команд |

XTAL1, XTAL2 |

2, 3 |

Вход и выход для подключения кварцевого резо- натора, а также вход для внешнего ГТИ |

T0 |

1 |

Тестовый вход или выход для выдачи импульсов CLK, формируемых внутри МК |

T1 |

39 |

Тестовый вход, а также вход для приема импуль- сов счета |

INT |

2 |

Тестовый вход, а также вход для приема внеш- него запроса на прерывание с низким уровнем ак- тивности |

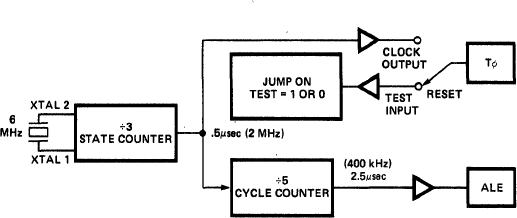

Встроенный в 8048 работает в диапазоне частот 1 –11 МГц. Вывод XTAL1 служит входом, a XTAL2 – выходом каскада усиления. Внешний квар- цевый резонатор или RC-цепочка подключаются к XTAL1, XTAL2, обеспечи- вая необходимую для генерации внешнюю связь и сдвиг фаз.

В результате деления частоты OSC на 3 получается основная тактовая частота CLK, определяющая работу внутренних узлов МК. Синхросигнал ма- шинных циклов ALE формируется путем дополнительного деления CLK на 5 и постоянно присутствует на одноименном выходе МК.

Рисунок 2 – Генерация сигналов в К1818ВЕ48

Каждый машинный цикл состоит из пяти тактов CLK, именуемых S1 – S5. Для выполнения команды требуется один или два машинных цикла. Прием команды всегда осуществляется в первом такте S1 первого машинного цикла M1. Во втором такте S2 принятая команда декодируется, a PC получает при- ращение. Такты S3 – S5 отводятся для внутреннего исполнения команды. В случае двухбайтовой или одноцикловой команды одновременно с этим память программ предъявляет новое значение PC. Новый элемент программной по- следовательности считывается в такте S1 следующего машинного цикла. Для одноцикловой команды S1 – начало нового командного цикла.

Во втором машинном цикле двухбайтовая команда считывает второй байт программной последовательности, представляющий либо непосред- ственные данные, либо младшую часть адреса. Функциональное распределе- ние тактов S1 – S5 аналогично М1. Однобайтовая двухцикловая команда с об- ращением к управляющей памяти во втором машинном цикле выполняется по аналогии с двухбайтовой. Все другие двухцикловые команды в такте S2 вто- рого машинного цикла считывают данные либо из внешнего ОЗУ, либо из пор- тов. В этом случае необходимая адресная информация передается в тактах S3

– S5 первого машинного цикла.

Входные сигналы всех портов совместимы с ТТЛ, а на выходах может быть подключена стандартная ТТЛ-нагрузка. Вывод данных через порты P1, P2 осуществляется в такте S5 второго машинного цикла. При работе с портом BUS операции ВВ сопровождаются генерацией импульсов RD, WR, которые

могут быть использованы для организации синхронного ВВ. Данные действи- тельны на срезе стробов.

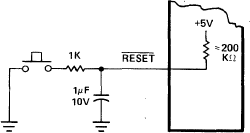

Вход RESET обеспечивает инициализацию процессора. Этот вход имеет внутренний подтягивающий резистор 200 кОм, который в сочетании с внеш- ним конденсатором 1 мкФ обеспечивает внутренний импульс сброса достаточ- ной длины, чтобы гарантировать сброс всех цепей. Если импульс сброса гене- рируется по нажатию кнопки, контакт RESET должен удерживаться на земле не менее 10 миллисекунд. Требуется 5 машинных циклов (12,5 мкс при 6 МГц), при условии, что питание МК уже включено.

Рисунок 3 – Организация сброса

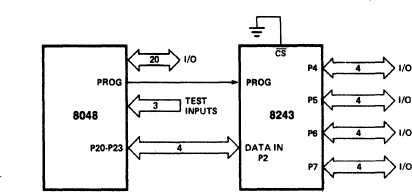

Интерфейс расширения ввода-вывода содержит 4-разрядную информа- ционную шину команд/данных Р20—Р23 и линию управления PROG. Интер- фейс активизируется по командам:

MOVD А, Рр MOVD Рр, А ORLD Рр, А ANLD Рр,А

Подключение микросхемы приведено на рис. 4.

Рисунок 4 – Подключение расширителя ввода–вывода

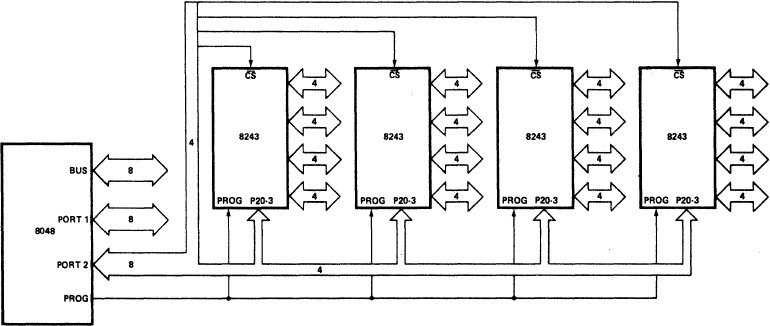

Рисунок 5 – Подключение 4-х расширителей ввода–вывода

Протокол интерфейса состоит в передаче через 4-разрядный канал Р2.0

– Р2.3 кода операции и данных обмена, которые однозначно связаны с че- тырьмя вышеуказанными командами. Управление обменом осуществляется с помощью сигнала PROG, срез которого синхронизирует передачу кода опера- ции обмена, а фронт – данных обмена.

В операциях участвует младшая тетрада аккумулятора. При чтении пор- тов старшая тетрада A сбрасывается. Система команд предусматривает выпол- нение периферийной операции логического AND и OR содержимого порта с состоянием младшей тетрады аккумулятора. Пользователь может по своему усмотрению интерпретировать эти команды и команды пересылки, внося но- вый смысл в их содержание. В отличие от цикла обращения к внешней памяти программ состояние младшей части порта Р2 после операций обмена с внеш- ней системой ввода-вывода не восстанавливается. После чтения Р2.0 – Р2.3 будут находиться в режиме ввода, после записи Р2.0 – Р2.3 содержат данные, переданные в канал. В случае недостатка каналов ввода-вывода возможно под- ключение нескольких микросхем расширителя. Пример подключения 4 рас- ширителей приведен на рис. 5.