Учебное пособие 800427

.pdfные принципы организации параллельных вычислительных систем реализуются в ар-

хитектуре вариантов, приведенных на рис. 2.5, б и г. На основе таких архитектур мультипроцессорных систем в соответствии с требуемыми задачами автоматизации производства возможно построение различных вариантов структур управления робо-

тотехническими комплексами оборудования. |

|

|

В простейшем случае при |

роботизации, например, |

механического участ- |

ка прессового оборудования |

для холодной штамповки |

в состав системы про- |

граммного управления группой цикловых ПР входят: пульт оператора, модули управ-

ления (микроЭВМ), памяти, дискретных команд входов-выходов и связи (микропро-

цессор) при необходимости выхода на следующий уровень управления. Роботизация механического участка металлорежущих станков с ЧПУ может потребовать дополнительно введения модулей интерполятора, управления приводами станка и робота, измерительного модуля и т. д.

Автоматизация операций на таком участке, связанных с загрузкой станка не-

ориентированными в пространстве заготовками, потребует, например, при использо-

вании средств технического зрения введения модуля предварительной обработки ви-

зуальной информации, модуля адаптивного управления и т. д.

Аналогично можно проследить видоизменением состава модулей программно-

го и адаптивного управления на уровне ячейки, участка при автоматизации основных технологических операций, таких как дуговая или контактно-точечная сварка, сборка изделий различной сложности, нанесение лакокрасочных покрытий и т. д.

Автоматизация транспортных и складских операций на данном уровне управ-

ления может отсутствовать, но она является необходимой и обязательной при перехо-

де на следующий иерархический уровень — групповое управление участком (лини-

ей).

Верхним уровнем управления при автоматизации линий, цехов, производств является автоматическая система управления технологическими процессами (АСУ ТП).

Таким образом, представленный набор средств управления позволяет компоно-

вать типовые управляющие комплексы и широкий спектр их модификаций для раз-

личных задач управления роботизированными производственными ячейками, участ-

ками, линиями и т. д.

3. Основные функциональные модули систем управления

В управляющих системах ПР независимо от их назначения, принципов струк-

турно-алгоритмической организации, информационно-вычислительных возможно-

стей и т. д. можно укрупненно выделить следующие основные функциональные мо-

дули: управляюще-вычислительный, программозадающий, сопряжения с манипу-

лятором, технологическим оборудованием и пульт управления.

Использование принципов блочно-модульного построения систем управления предполагает большую функциональную завершенность таких модулей с учетом расширенной их номенклатуры и степени сопряжения между собой.

Внутренний (межблочный) интерфейс системы обусловливается выбранной органи-

зацией управляюще-вычислительной части (процессора); он особенно ярко выражен в микропроцессорных системах управления, достаточно многообразен и может явиться предметом отдельного рассмотрения.

В данной главе акцентировано внимание на принципах построения блоков (мо-

дулей), функциональное назначение и сложность которых определяется применением их в различных цикловых и позиционно-контурных системах управления ПР.

3.1. Управляюще-вычислительные модули

В описанных ранее системах циклового программного управления (ЦПУ), по-

строенных по принципу жесткой реализации алгоритма управления, в качестве управляюще-вычислительного модуля использован микропрограммный автомат. Ос-

новной функцией такого модуля является формирование, в соответствии с требуемым алгоритмом, микроопераций (управляющих импульсов) для выдачи их в операцион-

ные узлы и другие функциональные блоки.

Задание микропрограммы в данном случае осуществляется обычно с помощью граф-

схемы или логической схемы алгоритма.

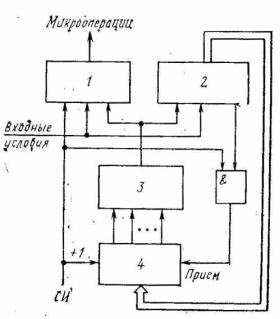

Примером структурной организации управляющего автомата на жесткой логи-

ке может служить схема, показанная на рис. 3.1. Собственно управляющий автомат со стоит из двух основных частей - памяти и комбинационной части.

Функционально комбинационная часть содержит: дешифратор состояний авто-

мата; схему формирования функций выхода; схему формирования функций возбуж-

дения.

Рис.3.1. Структурная организация управляющего автомата на жесткой логике:

1 – схема формирования выходных сигналов; 2 – схема формирования функций воз-

буждения; 3 – дешифратор состояний; 4 – буферный регистр; 5 – память возбужде-

ния; 6 – схема пуска-останова.

В большинстве случаев при построении управляющих автоматов пользуются

моделью автомата Миля, в которой выходные сигналы, вырабатываемые в процессе перехода из состояния в состояние, и сигналы возбуждения элементов памяти являются логическими функциями состояния автомата и набора входных логических

условий, поступающих с внешних по отношению к автомату операционных узлов.

Память автомата строится, как правило, |

по двухъярусной схеме и включает |

память возбуждений и буферный регистр. |

|

Синхронизация автоматов с двойной |

памятью производится с помощью |

двух последовательностей синхронизирующих импульсов СИ и СИ . Первая последо-

вательность импульсов обеспечивает работу комбинационной части, а вторая необходима для переписи состояния триггеров памяти возбуждений в буфер-

ный |

регистр. |

Для нормальной работы управляющего автомата в |

качестве до- |

|

полнительного |

узла в его состав обычно включают схему пуска-останова, которая |

|||

устанавливает |

в |

исходное состояние элементы памяти возбуждений при включе- |

||

нии питания или по сигналу пуска и открывает вентиль для выдачи |

синхронизи- |

|||

рующих сигналов на комбинационную часть. |

|

|||

|

Рассмотрим принцип работы данного автомата. |

|

||

|

При поступлении импульса запуска на схему пуска-останова формируется сиг- |

|||

нал сброса элементов памяти возбуждений в исходное состояние, которое по импуль-

су СИ переписывается в буферный регистр. Исходное состояние автомата далее де-

шифрируется и поступает на вход логических схем формирования выходных сигна-

лов и функций возбуждения, на которые также поданы потенциальные сигналы логи-

ческих условий, анализируемые автоматом по алгоритму. Схема пуска-останова от-

крывает вентиль, пропускающий на комбинационную часть тактирующую серию им-

пульсов (СИ). По первому импульсу этой серии комбинационной частью в соответст-

вии с граф-схемой алгоритма формируются: (вырабатываемые при переходе из ис-

ходного состояния) выходные сигналы, поступающие на операционные узлы, и сиг-

налы возбуждения элементов памяти, определяющие очередное состояние автомата.

По импульсу СИ сформированное состояние переписывается в буферный регистр,

дешифрируется и поступает на логические схемы комбинационной части, подготав-

ливая их к работе в очередном такте. В дальнейшем по мере подачи синхронизирую-

щих сигналов автомат, отрабатывая алгоритм, повторяет описанный цикл работы.

Рассмотренная структурная организация управляющего автомата является эф-

фективной при построении автоматов с большим числом состояний и сильно ветвя-

щимися алгоритмами.

При построении простых автоматов с относительно небольшим числом состоя-

ний (ориентировочно до 15-30) и в основном последовательным характером алгорит-

ма оказывается целесообразной структурная схема автомата, изображенная на рис.

3.2.

Для данной схемы характерно то, что в качестве памяти автомата используется асинхронный счетчик, обладающий свойствами двойной памяти. В этом случае отпа-

дает необходимость формирования функции возбуждения в ветвях алгоритма с по-

следовательными операторами. Ветвление алгоритма производится за счет записи

счетчиком кода требуемого состояния, который формируется с помощью шифратора,

функционально выделенного в комбинационной части. Код очередного состояния вырабатывается в зависимости от значения набора входных логических условий.

Сигнал загрузки счетчика при ветвлении формируется специальным вентилем, управ-

ляемым от шифратора очередного состояния.

Рис. 3.2. Структурная схема управляющего автомата со счетчиком состояний:

1 – схема формирования выходных сигналов; 2 – шифратор очередного состояния; 3 –

дешифратор состояния; 4 – счетчик состояний.

Организация такого управляющего автомата позволяет применить в качестве дешифратора и счетчика ИМС средней степени интеграции, что обеспечивает ком-

пактность аппаратной реализации. Другим направлением в реализации микропро-

граммных автоматов управления является использование их структурной организа-

ции на основе программируемой логики [29]. В основе таких автоматов лежит прин-

цип программного управления, в котором использована операционно-адресная струк-

тура управляющих слов. Управляющее слово определяет порядок функционирования автомата в течение одного такта (микрокоманда). Каждая микрокоманда содержит информацию о выдаваемых в такте микрооперациях и об адресе следующей микро-

команды.

Структура управляющего автомата с программируемой логикой изображена на рис. 3.3. Микропрограмма работы автомата хранится в ПЗУ, в каждой ячейке которо-

го записана одна микрокоманда. Считываемые из ПЗУ микрокоманды заносятся в

специальный регистр для текущего хранения на время одного такта. Каждая микро-

команда состоит из четырех информационных полей:

-номера выдаваемой в такте микрооперации;

-номера опрашиваемого логического условия;

-адресов для принудительной адресации очередной микрокоманды (А0 или А1).

Рис.3.3. Структурная схема управляющего автомата с программируемой логикой: 1 –

дешифратор микроопераций; 2 – коммутатор логических условий; 3 – коммутатор ад-

реса; 4 – распределитель импульсов.

Микрооперации формируются с помощью тактируемого дешифратора, подклю-

ченного к соответствующему регистру микрокоманд. Опрос логических условий про-

изводится коммутатором, адресуемым полем номера логического условия в регистре микрокоманд. Передача из регистра микрокоманд адресов А0 и А1 в регистр адреса

(РА) ПЗУ осуществляется с помощью коммутатора, управляемого с выхода коммута-

тора логических условий. В случае, если состояние опрашиваемого логического усло-

вия равно нулю, то в адресный тракт передается адрес А0, в противном случае — адрес А1.

Местное управление работой автомата осуществляется с помощью распредели-

теля тактирующих импульсов, работающего по жесткому циклу:

-чтение в регистр микрокоманд;

-тактирование дешифратора микроопераций;

-занесение в адрес очередной микрокоманды в РА ПЗУ.

Считанная из ПЗУ микрокоманда обрабатывается следующим образом. Код но-

мера микрооперации поступает на дешифратор, тактируемый от распределителя им-

пульсов. В момент прихода импульса «Выдача» формируется микроопераций, посту-

пающая в операционные узлы. При данной структуре автомата в каждом такте может выполняться не более одной микрооперации. После выполнения микрооперации осу-

ществляется переход к очередной микрокоманде по адресу А0 или А1; определяемому в результате анализа состояния условия с номером, указанным в микрокоманде. Ад-

рес перехода по импульсу «Запись в РА» вносится в регистр адреса ПЗУ. Управляю-

щие автоматы с программируемой логикой включают также схему пуска-останова.

Путем введения ряда дополнительных узлов можно обеспечить одновременную выдачу нескольких микроопераций и высокий коэффициент использования емкости ПЗУ. Среди достоинств данной структурной организации отметим возможность схемной реализации автомата на базе серийно выпускаемых СИС и БИС ПЗУ, что по-

зволяет существенно сократить аппаратурные затраты. Однако по сравнению с управ-

ляющими автоматами на жесткой логике автоматы с программируемой логикой обла-

дают более низким быстродействием.

Рассмотренные принципы структурной организации микропрограммных авто-

матов использованы при построении цикловых устройств УЦМ-30, УЦМ-663 и легли в основу управляюще-вычислительных модулей при создании позиционных уст-

ройств типа УПМ-772. Прогресс в развитии микропроцессорной техники выявил эф-

фективность использования в локальных и особенно групповых средствах программ-

ного управления промышленными роботами циклового и позиционно-контурного ти-

пов в качестве управляюще-вычислительных модулей микропроцессорных наборов и стандартных микроЭВМ различной конфигурации.

Структурная схема микроЭВМ содержит в общем случае пять основных частей:

микропроцессор, схемы формирования сигналов внутреннего интерфейса и тактиро-

вания, оперативно-запоминающее устройство (ОЗУ), ПЗУ и устройства ввода-вывода.

Ядром микроЭВМ является микропроцессор, состоящий из одной или несколь-

ких БИС, выполняющий функции по логической обработке информации. Организа-

ция микропроцессора ориентирована на достижение универсальности его использо-

вания, высокой производительности и технологичности.

Универсальность микропроцессоров (МП) определяется возможностью их раз-

нообразного применения и обеспечивается программным управлением МП и специ-

альными аппаратно-логическими средствами: использованием внутренней сверхопе-

ративной памяти, развитой системой прерывания, магистральной организацией внут-

ренних и внешних шин.

Принципиальной особенностью всех микропроцессорных систем является на-

личие унифицированного для модулей магистрального интерфейса, по которому они обмениваются информацией с процессором. Большинство МП самостоятельно не может формировать все системы внутрисистемного интерфейса из-за ограничений на число выводов корпуса микропроцессора и их ограниченной нагрузочной способно-

сти. Для зтой цели в составе микроЭВМ предусматривают специальные схемы, как правило, входящие в микропроцессорный набор. В ряде случаев специальные схемы приходится применять для формирования тактовых импульсов, синхронизирующих работу МП.

К внутреннему интерфейсу микроЭВМ подключены все основные функцио-

нальные узлы как самой микроЭВМ, так и все внешние по отношению к ней модули.

Программа, по которой работает микроЭВМ, хранится в постоянном запоминающем устройстве и не разрушается при отключении питания. Для хранения данных в соста-

ве микроЭВМ предусмотрено ОЗУ. Кроме ОЗУ и ПЗУ остальные функциональные узлы микроЭВМ по отношению к МП рассматриваются как устройства ввода-вывода,

в том числе блоки приоритетных прерываний, каналы последовательной передачи данных, программируемые таймеры и т. п.

Выбор типа микропроцессора для построения микроЭВМ производят на ос-

нове анализа технических требований, предъявляемых к функциям микроЭВМ, вы-

полняемым в управляющем устройстве. В цикловых устройствах на микроЭВМ в ос-

новном возлагаются функции логической обработки информации. МикроЭВМ выполняет также ряд вспомогательных функций по настройке программируемых БИС ввода-вывода, организации работы каналов последовательной передачи данных и т. п. Требования к быстродействию МП определяются организацией мультипро-

граммного режима работы микроЭВМ при одновременном управлении несколь-

кими координатами одного манипулятора и одновременном управлении несколь-

кими манипуляторами. При выборе типа МП следует учитывать возможности

организации развитой периферии, т. е. выбор БИС должен обеспечивать тре-

буемое и компактное построение всей микропроцессорной системы управления. По-

лучивший применение микропроцессорный набор типа КР580 имеет в своем составе

БИС контроллера прерываний, программируемого таймера, параллельного про-

граммируемого адаптера, контроллера прямого доступа в память и т. д. Собственно

микропроцессор рассматриваемого набора обладает развитой |

системой команд, |

|

позволяющей обрабатывать 8- и 16-разрядные |

слова, имеет |

удовлетворитель- |

ное быстродействие (время выполнения простых операций — 2 икс) и т. д. В пози- |

||

ционно-контурных системах управления на |

микроЭВМ возлагаются задачи об- |

|

работки информации: в контуре управления приводами, интерполяции, различных видов коррекций траектории и т. д. Для решения таких задач более эффективным оказывается микропроцессорный набор с процессором КР1810ВМ86. Успешное вы-

полнение задачи позиционно-контурного управления достигается также с применени-

ем стандартных микроЭВМ, например, типа «Электроника-60» или других различной производительности.

Рассмотрим структуру микроЭВМ на примере управляюще-вычислительного модуля, устройства циклового управления, построенного на базе МПН КР580 (типа УЦМ-100).

На рис. 3.4 приведены состав микроЭВМ и основные связи между функцио-

нальными узлами. Внутренний интерфейс микроЭВМ содержит:

-шину данных, по которой производится двунаправленный обмен данными между отдельными составными частями микроЭВМ;

-адресную шину, которая служит для адресации памяти и периферийного оборудования;

-управляющую шину, которая обеспечивает согласованную работу составных

частей микроЭВМ и управляет процессами передачи данных по внутренне-

му интерфейсу.

Обработка информации в микроЭВМ осуществляется микропроцессором типа КР580ИК80А.

Тактирование МП и управление внутренним интерфейсом производятся с по-

мощью ИМС КР580ГФ24 и КР580ВГ28. Генератор тактовых сигналов синхронизиру-

ет работу микропроцессора при помощи двух временных сигналов Ф1 и Ф2, выраба-

тывает ряд вспомогательных сигналов системного интерфейса, в том числе сигналы системного сброса и системной готовности. В функции генератора тактов входит также формирование сигнала приема слова-состояния в системный контроллер. По-

следний обеспечивает управление буфером шины данных процессора и формирова-

ние сигналов шины управления.

Для повышения нагрузочной способности адресной шины на выходе адресного тракта МП установлен буфер из шинных формирователей типа К589АМ6, настроен-

ных на передачу адресной информации от МП в шину адреса.

Микропроцессор, генератор тактов, системный контроллер и буфер адреса со-

ставляют ядро микроЭВМ. Проблемная ориентация микроЭВМ достигается за счет применения БИС МПН соответствующей функциональной номенклатуры и комплек-

тования микроЭВМ ОЗУ и ПЗУ необходимой емкости. В состав микроЭВМ при по-

строении управляющих систем входят обычно БИС блока приоритетных прерываний,

программируемого таймера и программируемого связного адаптера.

Блок приоритетных прерываний, реализованный на БИС КР580ВН59, предна-

значен для управления процессом обслуживания многоуровневых прерываний от раз-

личных блоков. Программируемый блок приоритетных прерываний увеличивает про-

пускную способность системы: одна БИС типа КР580ВН59 обеспечивает возмож-

ность обработки восьми сигналов — запросов прерывания. Путем каскадного вклю-

чения таких микросхем число запросов прерывания можно расширить до 64. Каждый сигнал блока соответствует определенному уровню прерывания. Приоритет различ-

ных уровней задается путем программирования и может быть «замаскирован» запи-

сью соответствующего кода в регистр маски, предусмотренный в микросхеме.

Включение блока приоритетных прерываний в состав микроЭВМ современных устройств управления ПР необходимо для решения задач группового управления ма-

нипуляторами в реальном масштабе времени и организации связи с ЭВМ верхнего ранга и терминалами. С этой же целью в состав микроЭВМ включают также про-

граммируемый таймер, обеспечивающий формирование временных задержек различ-

ного назначения.

Таймер содержит три 16-разрядных счетчика и схему управления, которая «на-

страивает» счетчики на различные режимы работы (деление частоты на заданное чис-

ло, отсчет определенной выдержки времени и т. п.). Режимы работы задаются путем