контрольнная работа

.docx3.2. Шифраторы, дешифраторы и преобразователи кодов: назначения, виды, функционирование, принципы построения

Шифраторы (кодеры) – устройства, предназначенные для преобразования алфавитно-цифровой информации, поданной унитарным n-разрядным кодом в эквивалентный двоичный m-разрядный код. Особенностью унитарного кода является активное состояние только одной переменной Xi входного набора {Xn-1…X1 X0}, порядковый номер i которой подлежит кодированию. Т.е. шифратор n-m – это преобразователь унитарного кода «1 из n» в двоичный (параллельный) код, у которых число выходов mоднозначно связано с числом входов n как 2m. При n =2m используется полный набор выходных двоичных комбинаций Yi. Такой шифратор называется полным. Например, шифратор 8-3 полный, т.к. он реализует полный набор возможных комбинаций переменных Xi(n=8) в полный выходной набор Yi(m=3) как 23=8.

В неполном шифраторе число входов n не соответствует числу всех возможных выходных комбинаций 2m (n <2m), что соответственно создает некоторое число неиспользованных выходных наборов. Примером неполного шифратора является шифратор 10-4, используемый для кодирования десятичных чисел в двоичный код (8-4-2-1).

При синтезе полного (неполного) шифратора достаточно реализовать в заданном базисе систему логических функций Yi, которые создают на его m выходах слово {Ym-1 …Y1 Y0}. Например, полный шифратор 8-3 описывается таблицей истинности (табл. 3.1) и системой логических функций:

![]() ;

;![]()

![]() ;

(3.1)

;

(3.1)

![]() .

.

Таблица 3.1 Таблица истинности полного шифратора 8-3

|

Число |

Входы |

Выходы |

||||||||||

|

X0 |

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

Y2 |

Y1 |

Y0 |

||

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

4 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

5 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

|

6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

|

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

Из системы логических функций следует, что шифратор 8-3 реализуется в базисе ЛЭ 4ИЛИ (рис. 3.1). Y0 - выход младшего разряда весом 20, Y1 - 21 и Y2 – выход старшего разряда весом 22.

Неполный шифратор реализуется аналогично полному, однако, отсутствуют те наборы переменных, которые не используются при кодировании. В шифраторе 10-4 неиспользованных выходных наборов будет 24-10=6 – Yi:{1010}, {1011}, {1100}, {1101}, {1110}, {1111}.

Приведенный на рис. 3.1 шифратор – линейный, все ЛЭ присоединяются к одной общей шине (линии). Для реализации линейного шифратора необходимо иметь многовходовые ЛЭ. Переменная X0 не задействована (табл. 3.1). Это означает, что при любом сигнале на входе X0 на выходе шифратора не будет никаких изменений.

Рис. 3.1. Схема функциональная полного шифратора

Меньшим быстродействием кодирования обладают пирамидальные шифраторы, построенные по принципу использования однотипных, например, двухвходовых ЛЭ 2И-НЕ. Структурная схема таких шифраторов похожа на пирамиду. Число ЛЭ не зависит от разрядности m кодированного слова.

В линейных и пирамидальных шифраторах реализуется обязательное соответствие выходного m-разрядного кода одному активному входу. Чтобы шифратор реагировал только на один из нескольких активных входов, его схему строят по приоритетному принципу.

В приоритетном шифраторе выходной код всегда соответствует тому активному входу, который имеет наибольший номер набора. Например, на выходе приоритетного шифратора при активных входах Х1, Х2, Х4 появится код {100}, что соответствует переменному Х4 (активные входы Х1 и Х2 игнорируются).

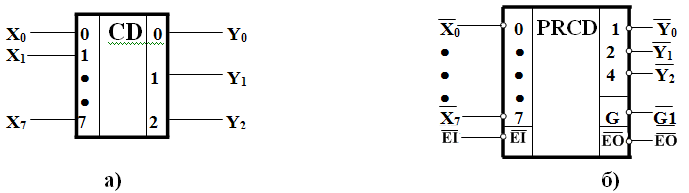

Рис.3.2. Условное графическое изображение полного (а) и приоритетного (б) шифраторов

В промышленных сериях элементов имеются шифраторы приоритета для восьмиразрядных и десятиразрядных слов. Функционирование восьмиразрядного приоритетного шифратора описывается таблицей истинности (табл. 3.2).

Таблица 3.2 Таблица истинности восьмиразрядного приоритетного

шифратора

|

EI |

X7 |

X6 |

X5 |

X4 |

X3 |

X2 |

X1 |

X0 |

Y2 |

Y1 |

Y0 |

G |

EO |

|

1 1 1 1 1 1 1 1 1 0 |

1 0 0 0 0 0 0 0 0 X |

X 1 0 0 0 0 0 0 0 X |

X X 1 0 0 0 0 0 0 X |

X X X 1 0 0 0 0 0 X |

X X X X 1 0 0 0 0 X |

X X X X X 1 0 0 0 X |

X X X X X X 1 0 0 X |

X X X X X X X 1 0 X |

1 1 1 1 0 0 0 0 0 0 |

1 1 0 0 1 1 0 0 0 0 |

1 0 1 0 1 0 1 0 0 0 |

1 1 1 1 1 1 1 1 0 0 |

0 0 0 0 0 0 0 0 1 0 |

Таблица 3.2 характеризует работу приоритетного шифратора при всех возможных комбинациях сигналов. На рисунке 3.2,б показано его условное графическое изображение, сигнал EI – разрешение работы шифратора; ЕО – сигнал, вырабатываемый на выходе шифратора при отсутствии запросов на его входах, служит для разрешения работы следующего (младшего) шифратора при наращивании размерности шифраторов; G – сигнал, отмечающий наличие запросов на входе; Х0…Х7 – запросы на входах; Y2…Y0 – значения разрядов выходного двоичного кода, формируемые по номеру старшего активного запроса. Все перечисленные сигналы формируются при условии ЕI=1 (работа разрешена). При ЕI=0 независимо от состояния входов запросов все выходные сигналы становятся нулевыми.

Из таблицы 3.2 можно записать выражения для Y2, Y1, Y0, EO и G:

![]()

![]()

![]()

![]() (3.2)

(3.2)

![]() ;

;

![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]() .

.

Линейные шифраторы используются для передачи информации в интерфейсных устройствах, при сжатии информации, передаваемой с помощью малого числа линий связи.

Приоритетные шифраторы могут использоваться для цифро-аналогового и аналого-цифрового преобразования, а также для реализации приоритетного кодирования и прерывания в микропроцессорной схемотехнике.

Дешифраторы (декодеры) – устройства для распознавания числа, поданного позиционным n-разрядным кодом. Дешифраторы относятся к преобразователям кодов. Дешифратор n-m выполняет функцию преобразования двоичного кода в унитарный код «1 из m», т.е. выполняет функцию, обратную шифратору. Для полного дешифратора m=2n, где m – порядковый номер выхода Yiдешифратора. В неполном дешифраторе число выходов m не соответствует 2n (m<2n).

В условном графическом обозначении (рис. 3.3,б) входы дешифратора обозначают их двоичными весами. Помимо информационных входов дешифратор обычно имеет один или более входов разрешения работы (EN). При наличии разрешения по этому входу, дешифратор работает описанным выше образом, при его отсутствии – все выходы дешифратора пассивны. Если входов разрешения несколько, то сигнал разрешения работы образуется как конъюнкция сигналов отдельных входов разрешения. Часто дешифратор имеет инверсные выходы. В этом случае только один выход имеет нулевое значение, а все остальные – единичное, а при запрещении работы на всех выходах будет присутствовать логическая единица. Функционирование полного дешифратора (n – m) описывается системой (3.3):

![]() ;

;

![]() ;

;

![]() ;

;

……………………………………………………;

![]() .

.

Как следует из системы конъюнкции (3.3), каждому из m выходов полного дешифратора соответствует одна из 2n кодовых комбинаций (минтерм или макстерм) n - разрядного входного слова {Xn-1…X1 X0}.

В неполном дешифраторе есть некоторое число неиспользованных входных наборов.

Схемы полного или неполного дешифраторов так же, как и шифраторов, можно собрать по линейной или пирамидальной структуре.

Число выходов полного четырехразрядного дешифратора равно 16 (24=16). Полный дешифратор 4-16 описывается системой булевых функций (3.4):

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

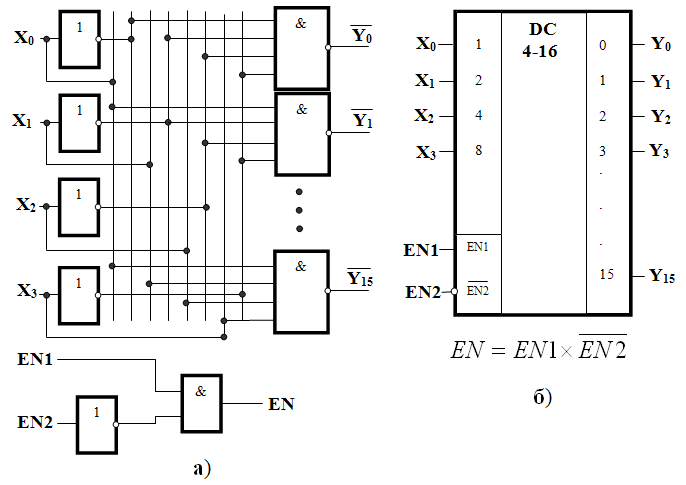

На рисунке 3.3,а представлена схема функциональная полного дешифратора 4-16, функционирующего в соответствии с таблицей 3.3.

Рис. 3.3. Схема функциональная полного дешифратора 4-16 (а), условное графическое обозначение двоичного дешифратора 4-16 (б)

Таблица 3.3 Таблица истинности полного дешифратора 4-16

|

X3 |

X2 |

X1 |

X0 |

Yi |

|

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

1 |

|

|

0 |

0 |

1 |

0 |

|

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

|

|

0 |

1 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

|

|

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

|

|

1 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

0 |

|

|

1 |

1 |

1 |

1 |

|

В случаях, когда необходимо создать дешифратор на большее число выходов на основе дешифраторов с меньшим числом выходов, используют принцип наращивания. Он заключается в том, что данные входы дешифраторов разбивают произвольным образом на группы, каждая из которых реализует свою группу логических функций.

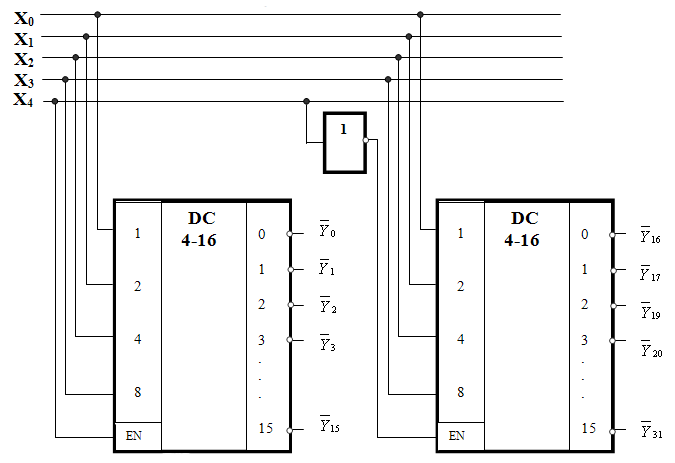

Рис. 3.4. Схема функциональная двухкаскадного дешифратора

На

рисунке 3.4 приведено двухкаскадное

соединение двух дешифраторов. Первый

каскад работает при активных входах Х0,

Х1,

Х2 и Х3 при

условии, что Х4=0.

Как только на входах дешифратора появится

код ![]() ,

первый каскад закроется, т.к.

,

первый каскад закроется, т.к.![]() ,

откроется второй каскад, получающий

через инвертор разрешающий уровень

,

откроется второй каскад, получающий

через инвертор разрешающий уровень![]() .

.

Дешифраторы используются в устройствах визуальной индикации, совместно со схемами ИЛИ их можно использовать для воспроизведения произвольных логических функций.

Линейные дешифраторы обеспечивают преобразование кода с минимальной задержкой и используются в наиболее быстродействующих цифровых схемах. Однако с ростом разрядности входного кода быстро возрастает нагрузка каждого из входов и количество корпусов интегральных микросхем (ИМС) для реализации дешифратора. Линейная структура обычно используется для построения дешифраторов с количеством входов ≤4.

Если число входов >4, то с целью уменьшения количества корпусов ИМС, дешифраторы выполняются по многоступенчатой схеме. Такие дешифраторы называются пирамидальными. Первой ступенью пирамидального дешифратора является простейший линейный дешифратор. Каждая последующая ступень, управляемая дополнительной входной переменной, позволяет удвоить количество выходов, т.е. k -ступенчатый полный пирамидальный дешифратор имеет число выходов N=2k+1, причем k=m-1 (при m=2 линейный и пирамидальный дешифраторы совпадают).

Преобразователи кодов применяют для преобразования двоичных кодов в двоичный дополнительный, двоично-десятичный, коды знаков русского или латинского алфавита, коды чисел любой системы счисления и наоборот.

Принцип построения преобразователей кодов рассмотрим на примере преобразования кода 8421 в код 2421. Обозначим переменные, соответствующие отдельным разрядам кода 8421, – Х4Х3Х2Х1, а кода 2421 – Y4Y3Y2Y1. В таблице истинности (табл. 3.4) приведено соответствие комбинаций обоих кодов.

Таблица 3.4 Таблица истинности преобразователя кода 8421 в код 2421

|

Код 8-4-2-1 |

Код 2-4-2-1 |

|

X4 X3 X2 X1 |

Y4 Y3 Y2 Y1 |

|

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

Каждая

из переменных Y4,Y3,Y2,Y1 может

рассматриваться функцией аргументов Х4,

Х3,

Х2,

Х1 и,

следовательно, представлена через эти

аргументы соответствующим логическим

выражением. Для получения указанных

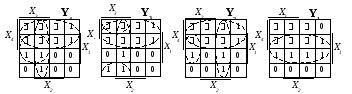

логических выражений, представим

переменные Y4,Y3,Y2,Y1 таблицами

истинности в форме карты Карно (рис.3.5)

Рис. 3.5. Карты Карно для преобразователя кода 8-4-2-1 в код 2-4-2-1

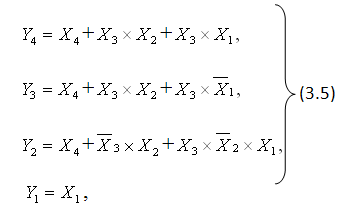

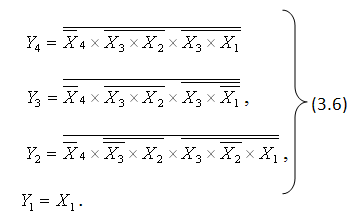

По картам Карно получаем минимальную форму логических выражений в базисе И, ИЛИ, НЕ (3.5) и, выполнив преобразования 3.5, воспользовавшись правилом де Моргана, получаем эти же выражения в базисе И-НЕ (3.6).

На рисунке 3.6 приведена логическая структура преобразователя кодов, построенная на элементах И-НЕ с использованием