СхТ_ЛР_5_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №5

по дисциплине «Схемотехника»

Тема: Компаратор

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 5. КОМПАРАТОР

Цель работы

Спроектировать компаратор в среде разработки, проверить его работоспособность.

Техническое задание

Цифровые компараторы – это КЦУ, предназначенные для сравнения двух двоичных чисел.

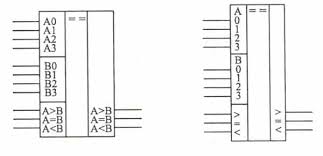

Обычно компаратор имеет входы наращивания разрядности, куда подключаются выходы результатов сравнения от другого компаратора. Это позволяет увеличивать разрядность сравниваемых чисел. Пример схемы типичного цифрового компаратора приведено на рисунке 1:

Рисунок 1 – Цифровой компаратор

В микросхемах цифровых компараторов предусмотрен дополнительный вывод для подачи сторнирующего сигнала Е {enable), который используется как для включения/выпадения компараторов, так и для каскадирования.

Работу цифрового компаратора можно представить следующим словесным описанием:

Если число А больше числа В, то активный уровень присутствует на выходе «А>В»;

Если число А меньше числа В, то активный уровень присутствует на выходе «А<В»;

Если число А равно числу В, то активный уровень без изменения копируется с одного из входов результата сравнения («А>В», «А=В» или «А<В») на одноимённый выход. При этом активный уровень должен присутствовать только на одном из этих входов.

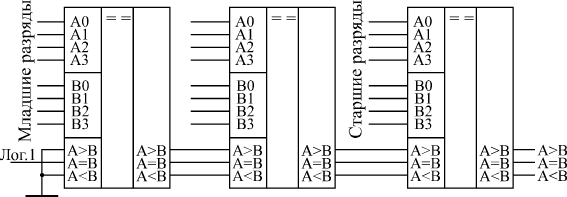

Если используется одиночная микросхема, то для ее правильной работы достаточно подать единицу на вход A = B, а состояния входов A<B и A>B не важны, на них можно подать как нуль, так и единицу. Если микросхемы компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то надо выходные сигналы микросхемы, обрабатывающей младшие разряды кода, подать на одноименные входы микросхемы, обрабатывающей старшие разряды кода (рисунок 2).

Рисунок 2 – Схема увеличения разрядности цифрового компаратора

Одно из основных применений компараторов кодов состоит в селектировании входных кодов. В этом случае достаточно иметь информацию только о совпадении кодов на входах компаратора, а не о соотношении их величин. Интересующий нас код (эталонный) подается на один вход компаратора, а изменяющийся код (входной) – на другой вход. Используется только выход равенства кодов А = В.

Микросхемы, выполняющие функции цифрового компаратора, кодируются буквами СП.

3. Теоретическая подготовка

Описание схемы:

Вход: 2 входных двоичных данных (A и B), сигнал блокировки(ENABLE), тактирующий вход (clk);

Выход: выходные сигналы Q1, Q2, Q3

Q1(A > B)

Q3(A < B)

Q2(A = B)

B

A

ENABLE

clk

Рисунок 3 – Схема цифрового компаратора

Работа модуля:

- Сигнал импульса (clk) дает входную частоту.

- Сравнит 2 входных данных.

- Q1 = ‘1’ при А > B, иначе Q1 = ‘0’.

- Q2 = ‘1’ при А = B, иначе Q2 = ‘0’.

- Q3 = ‘1’ при А < B, иначе Q3 = ‘0’.

Входы |

Выходы |

|||

A |

B |

Q1 |

Q2 |

Q3 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

Таблица 1 – Истинности однобитного компаратор

Код программы:

`timescale 1ns / 1ps

module comparator (

input wire [7:0] a,

input wire [7:0] b,

output reg equal,

output reg lower,

output reg greater

);

always @* begin

if (a<b) begin

equal = 0;

lower = 1;

greater = 0;

end

else if (a==b) begin

equal = 1;

lower = 0;

greater = 0;

end

else begin

equal = 0;

lower = 0;

greater = 1;

end

end

endmodule

module tb_comporator();

reg [7:0] a;

reg [7:0] b;

wire eq;

wire lw;

wire gr;

comparator uut (

.a(a),

.b(b),

.equal(eq),

.lower(lw),

.greater(gr)

);

initial begin

a=0;

b=0;

#100;

end

always begin #1 a=a+1; end

always begin #256 b=b+1; end

endmodule

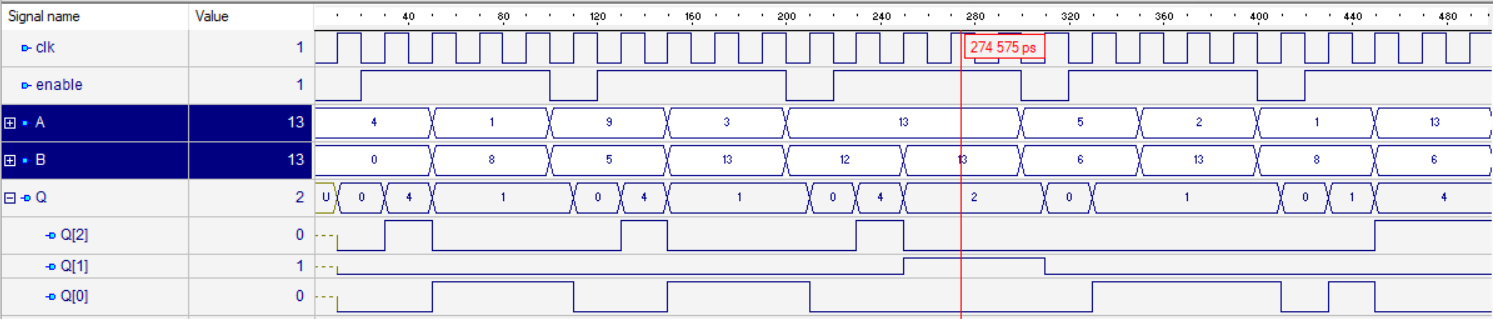

Временная диаграмма реализации схемы

Вывод

В результате выполнения лабораторной работы мы спроектировали компаратор в среде Quartus и проверили его работоспособность.