СхТ_ЛР_4_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №4

по дисциплине «Схемотехника»

Тема: Память

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 4. ПАМЯТЬ

Цель работы

Спроектировать в среде разработки модуль памяти с произвольным доступом, проверить работоспособность.

Техническое задание

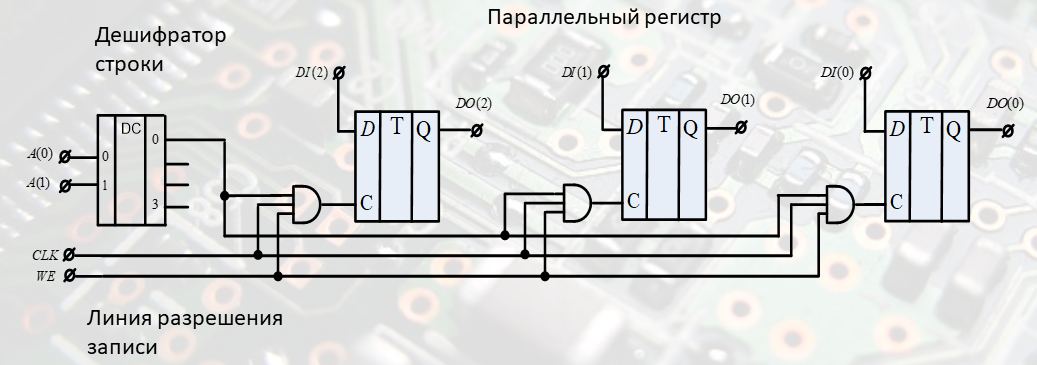

Основу памяти составляют двоичные слова и схема их выбора. Двоичное слово еще называют ячейкой памяти. По состоянию шины адреса происходит активация той или иной ячейки памяти и в зависимости от состояния линии разрешения можно считать или записать данные в ячейку.

Рисунок 1 - Устройство строки памяти

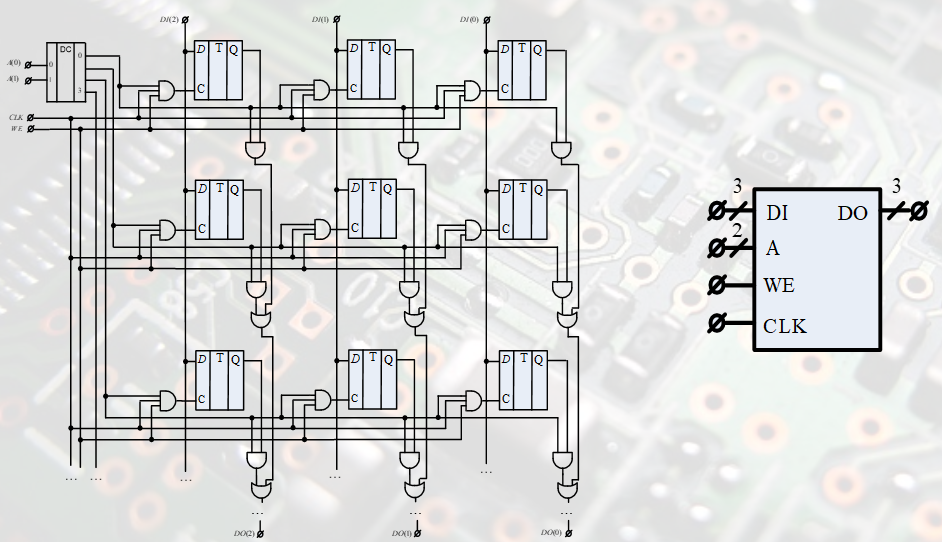

Самый простой модуль памяти имеет шину данных. Для выборки нужной ячейки необходима шина адреса (A). При помощи линии разрешения записи (WE) можно произвести сохранение информации в память. Для общей синхронизации всех процессов в проекте необходим вход тактовых сигналов (CLK).

Р исунок

2 - Устройство RAM память

исунок

2 - Устройство RAM память

Код программы:

`timescale 1ns / 1ps

module ram #(parameter N = 6, M = 32)

(input clk,

input we,

input wire [N-1:0] adr,

input wire [M-1:0] din,

output wire [M-1:0] dout

);

reg [M-1:0] mem[2**N-1:0];

always @(posedge clk)

if (we) mem[adr] <= din;

assign dout = mem[adr];

endmodule

`timescale 1ns / 1ps

module tb_ram;

reg clk;

reg [5:0] adr;

reg [31:0]din;

reg we;

wire [31:0]dout;

ram uut (

.clk(clk),

.adr(adr),

.din(din),

.dout(dout),

.we(we)

);

initial begin

clk = 0;

adr = 1;

din = 0;

we = 1;

#100;

end

always begin #5 clk = ~clk; end

always begin we =~we; #100; end

always begin #10 din=din+1;

adr = adr + 1; end

endmodule

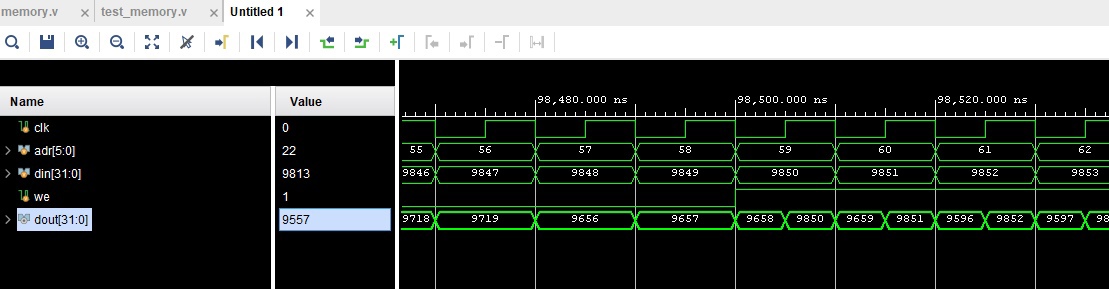

Временная диаграмма реализации схемы

Вывод

В результате выполнения лабораторной работы мы спроектировали модуль памяти в среде Quartus и проверили его работоспособность.