СхТ_ЛР_6_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №6

по дисциплине «Схемотехника»

Тема: Накапливающий сумматор

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 6. НАКАПЛИВАЮЩИЙ СУММАТОР

Цель работы

Спроектировать схему накапливающего сумматора в среде разработки, проверить работоспособность.

2. Основные теоретические положения

Сумматор — в кибернетике - устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов; устройство, производящее операцию сложения.

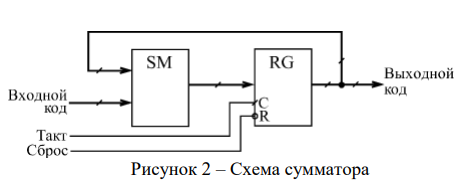

Накапливающие сумматоры состоят из комбинационных сумматоров и регистров, имеют более сложную структуру построения. Принцип их работы заключается в том, что сигнал на его выходе формируется только после операции сложения, а результат операции запоминается в самом сумматоре

Накапливающий сумматор состоит из сумматора и выходного регистров, охваченных обратной связью.

То есть на один вход сумматора подается код с выходов регистра, а на другой вход - входной код.

В результате с каждым следующим фронтом тактового сигнала в регистр записывается код суммы входного кода с предыдущим содержимым регистра, с предыдущей суммой.

3. Теоретическая подготовка

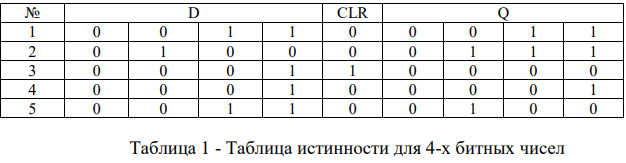

В этой реализации программы число D подается на вход после каждого синхроимпульса, если это число отличается от ранее введенного, то оно добавляется к текущей сумме. Текущая сумма выводится на выход Q. Если необходимо сложить два одинаковых числа, то вам нужно передать между этими двумя числами 0. Сумма сбрасывается подачей сигнала «CLR» = 1 (изначально этот сигнал = 0 ).

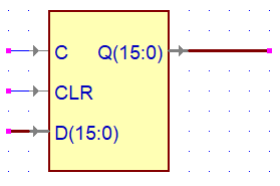

Рисунок 1 - Структурная схема

Код программы:

`timescale 1ns / 1ps

module nak_sym(

input wire[7:0]a,

input c,

input reset,

output reg[7:0]s

);

always@(posedge c or posedge reset)

begin

if (reset) begin

s=0;

end

else begin

s=s+a;

end

end

endmodule

module test_n_sym;

reg [7:0]a;

wire [7:0]s;

reg c;

reg reset;

nak_sym uut(

.a(a),

.s(s),

.c(c),

.reset(reset)

);

initial begin

a=0;

c=0;

reset=1;

#100;

end

always begin #15 c=1; #15 c=0; end

always begin #20 a=a+1; end

always begin #10 reset=0; #200 reset=1; end

endmodule

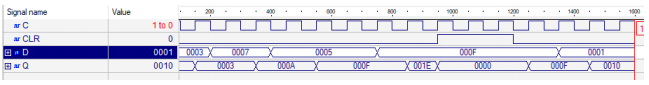

Временная диаграмма реализации схемы

Вывод

В результате выполнения лабораторной работы мы спроектировали накапливающий сумматор в среде Quartus и проверили его работоспособность.