книги / Схемотехника

..pdf

8.1. МОДЕЛИРОВАНИЕ ЛОГИЧЕСКОГО ЭЛЕМЕНТА ДЛЯ РЕАЛИЗАЦИИ СИСТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ В ПЛИС – FPGA – ДЕШИФРАТОРА DC – LUT2

Выполним моделирование одного разряда дешифратора DC – LUT2 для n = 2 в системе схемотехнического моделирова-

ния NI Multisim 10 фирмы National Instruments Electronics Workbench Group.

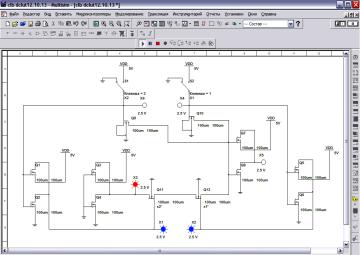

На рис. 8.5 ключи S1, S2 моделируют переменные Х1, Х2. Ключ S1 через инвертор Х2 (транзисторы Q1, Q2) управляет передающим транзистором Х2’ (Q11). Ключ S2 через инвертор Х1 (транзисторы Q5, Q6) управляет передающим транзистором Х1’ (Q12). Инвертор на основе транзисторов Q3, Q4 обеспечивает логическую единицу в цепочку Х2’, Х1’.

Рис. 8.5. Моделирование одного разряда дешифратора DC – LUT для n = 2 – последовательная цепочка не Х1,

не Х2 активизирована

111

Одновременно ключи S1, S2 управляют альтернативными цепочками КНФ – S1 – передающим транзистором Х2 (Q9), S2 – передающим транзистором Х1 (Q10), которые передают нулевой потенциал к выходному инвертору (Q7, Q8), если на их затворы подана единица, так что к нему всегда приложена одна единственная активная цепочка.

На рис. 8.5 последовательная цепочка не Х1, не Х2 активизирована, и именно она формирует логическую единицу на вход инвертора (Q7, Q8).

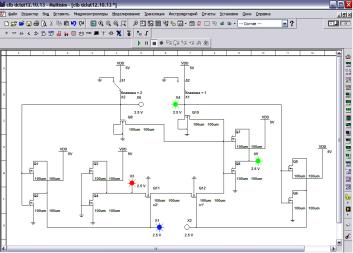

На рис. 8.6 представлено моделирование неактивной цепочки не Х1, не Х2 – ноль на затворе транзистора Х2’ (Q12), логический ноль передаётся транзистором Х1 (Q10), затворы транзисторов Q9, Q12 обнулены.

Рис. 8.6. Моделирование одного разряда дешифратора DC – LUT (для n = 2 – последовательная цепочка не Х1,

не Х2 не активизирована – не Х1 = 0)

112

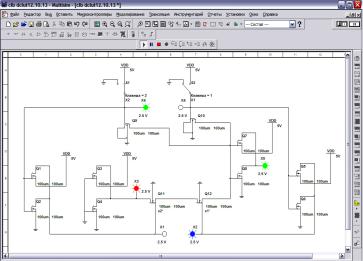

На рис. 8.7 представлено моделирование неактивной цепочки не Х1, не Х2 – ноль на затворе транзистора Х1’ (Q11), логический ноль передаётся транзистором Х2 (Q9).

Рис. 8.7. Моделирование одного разряда дешифратора DC – LUT (для n = 2 – последовательная цепочка не Х1, не Х2

не активизирована – не Х2 = 0)

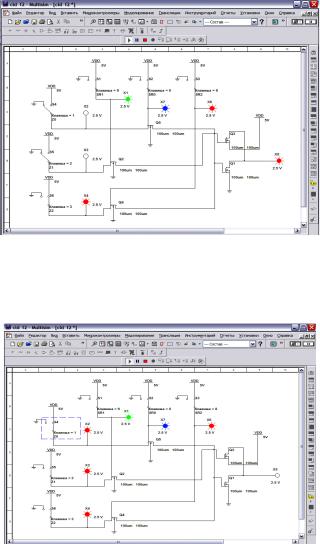

Выполним моделирование блоков программирования систем функций. Моделирование дизъюнкции трёх разрядов (0,1,2) дешифратора DC – LUT с инверсными выходами – реализация одной логической функции системы z0’, z1’, z2’ = 1 SR0,1,2 – значение конфигурационной памяти (рис. 8.8).

На рис. 8.8 имеется два активных нуля z0’ = 0, z1’ = 0, z2’ = 1, поэтому функция равна 1 (Х5 подключена через инвертор Q1, Q3).

Вслучаееслиz0’ = 1, z1’ = 1, z2’ = 1, то z0’, z1’, z2’ = 0 (рис. 8.9).

Выполненное моделирование подтверждает работоспособность предлагаемого технического решения DC – LUT, на которое получен патент РФ [17].

113

Рис. 8.8. Моделирование дизъюнкции трёх разрядов (0,1,2) дешифратора DC – LUT с инверсными выходами – реализация одной логической функции системы z0’, z1’, z2’ = 1, SR0,1,2 – значение конфигурационной памяти

Рис. 8.9. Моделирование дизъюнкции трёх разрядов (0,1,2) дешифратора DC – LUT (с инверсными выходами реализация одной логической функции системы z0’, z1’, z2’ = 0 SR0,1,2 – значение конфигурационной памяти)

114

9. ДНФ-LUT

Недостатком рассмотренных выше LUT является то, что они реализуют логические функции в СДНФ. Предлагается ДНФ конфигурируемый LUT.

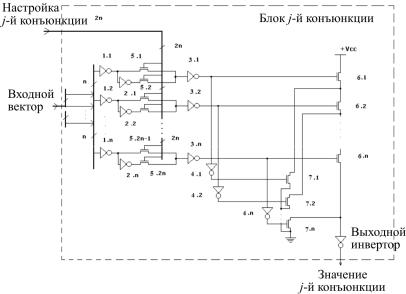

ДНФ-LUT представляет собой конфигурируемую пользователем структуру, аналогичную программируемой логической матрице ПЛМ [1, 5], для программирования которой необходим специальный программатор. В случае ДНФ-LUT конфигурирование предполагается таким же, как и в обычном LUT, путём загрузки оперативной памяти ОЗУ (SRAM). На рис. 9.1 представлена структура ДНФ-LUT, настройка конъюнкций загружается в SRAM, не указанную на рис. 9.1.

Рис. 9.1. Структура ДНФ-LUT

Таким образом, вместо загрузки значений таблицы истинности программируются лишь значения конъюнкций длиной n, где n – число переменных m логических функций.

Вхождения k конъюнкций в m функций также программируется настройкой функций. По заданному входному набору

115

(вектору) n переменных блоки конъюнкций вычисляют значения k конъюнкций, которые далее формируют «по ИЛИ» значения m логических функций. Рассмотрим внутреннюю структуру блоков конъюнкций и функций.

9.1.СТРУКТУРА БЛОКОВ КОНЪЮНКЦИЙ

ИФУНКЦИЙ ДНФ-LUT

Структура блока конъюнкции [6] ДНФ-LUT изображена на рис. 9.2.

Рис. 9.2. Структура блока конъюнкции ДНФ-LUT

Для задания значения одной из n переменных в j-й конъюнкции из k конъюнкций используются три группы инверторов 1, 2, 3, 4, так что если переменная входит в конъюнкцию без инверсии, то активируются нечётные транзисторы группы

116

5 транзисторов. Соответственно активируются затворы транзисторов группы 6. Если переменная входит в конъюнкцию с инверсией, то активируются чётные транзисторы группы 5 транзисторов. В случае несущественной переменной активируются и чётные, и нечётные транзисторы в каждой из пар группы 5, чтобы соответствующий транзистор в группе 6 был активирован. Если во входном наборе переменная не равна заданному значению, то соответствующий транзистор в группе 6 не будет активирован, но для исключения «третьего состояния» в цепочке транзисторов 6 с помощью инверторов группы 4 на его выход будет подключен потенциал «Ноль вольт», т.е. обеспечивается требуемая ортогональность сигнала на выходах транзисторов группы 6 [5].

Таким образом, в случае равенства данной конъюнкции единице на выходе будет ноль, иначе – единица. Для обеспечения ограничения по числу последовательно соединённых транзисторов [3] могут быть введены дополнительные промежуточные инверторы.

Так, для суммы по модулю два трёх переменных S0 S1 S2 настройка показана в табл. 9.1.

Таблица 9 . 1

Активирование транзисторов группы 5 четырёх блоков конъюнкции ДНФ-LUT для суммы по модулю два трёх переменных S0 S1 S2

№блока |

5.1 |

5.2 |

5.3 |

5.4 |

5.5 |

5.6 |

Конъюнкция |

||

конъюнкции |

|||||||||

1 |

0 |

1 |

0 |

1 |

1 |

0 |

(неS0) |

(неS1) (S2) |

|

2. |

0 |

1 |

1 |

0 |

0 |

1 |

(неS0) |

(S1) |

(неS2) |

3 |

1 |

0 |

0 |

1 |

0 |

1 |

(S0) (неS1) |

(неS2) |

|

4 |

1 |

0 |

1 |

0 |

1 |

0 |

(S0) |

(S1) |

(S2) |

Структура блока функций [6] ДНФ-LUT изображена на рис. 9.3.

117

Рис. 9.3. Структура блока функции ДНФ-LUT

Для задания необходимых конъюнкций для блока функции ДНФ-LUT используется внешняя настройка, активирующая затворы транзисторов Т. В случае хотя бы одного требуемого логического нуля по входу значений конъюнкций на выходе блока формируется логическая единица. Пример реализации двух функций – суммы по модулю два трёх переменных S0 S1 S2 и функции «одна единица в наборе S0, S1, S2» в двух блоках функций ДНФ-LUT представлен в табл. 9.2.

Таблица 9 . 2

Активирование транзисторов Т двух блоков функций ДНФ-LUT для суммы по модулю два трёх переменных S0 S1 S2

и функции «одна единица в наборе S0, S1, S2»

№ |

Тi.1 |

Тi.2 |

Тi.3 |

|

Тi.4 |

Функция |

|

1 |

1 |

1 |

1 |

|

1 |

i = 1; S0 S1 S2 |

|

2 |

1 |

1 |

1 |

|

0 |

i = 2; однаединицавнабореS0, S1, S2 |

|

|

9.2. СРАВНИТЕЛЬНАЯ ОЦЕНКА СЛОЖНОСТИ ДНФ-LUT |

|

|||||

|

Оценим сложность известного LUT: |

|

|||||

|

|

|

|

L = 2n 8 + 2n+1 + 2n, |

(9.1) |

||

|

|

|

|

|

n |

|

|

где 2n 8 – сложность настройки (по каждому входу настройки необходимо 6 транзисторов SRAM+2 транзистора – инвертор на

118

входе дерева передающих транзисторов); 2n – сложность инвер-

торов по n переменным; 2n+1 – сложность дерева передающих транзисторов с выходным инвертором.

В предлагаемом устройстве на один разряд из n разрядов требуется в блоке конъюнкций 12 транзисторов +2 транзистора на отдельный инвертор блока конъюнкции. На каждый из m блоков вычисления функций требуется k транзисторов +2 транзистора на отдельный инвертор блока вычисления функций. Итого, получаем:

L (n, k, m, SRAM) = k(12 n + 2) + m (k + 2) + 6k(2n) + 6mk, (9.2)

dnf

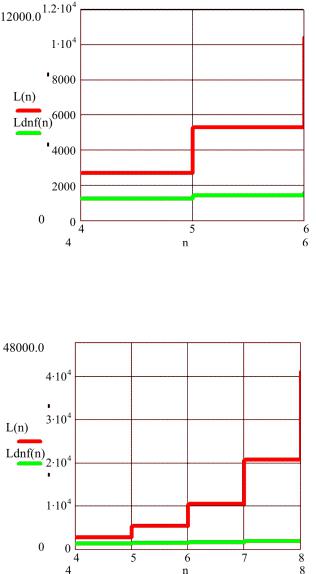

где n – число переменных, m-число функций, k – число конъюнкций. Сравнение сложности ДНФ-LUT (Ldnf(n)) и LUT (L(n)) для некоторых значений параметров представлены на рис. 9.4–9.6.

Рис. 9.4. Сравнение сложности ДНФ-LUT (Ldnf(n))

и LUT (L(n)) для n 2–4, m = 16, k = 8

119

Рис. 9.5. Сравнение сложности ДНФ-LUT (Ldnf(n))

и LUT (L(n)) для n 4–6, m = 16, k = 8

Рис. 9.6. Сравнение сложности ДНФ-LUT (Ldnf(n))

и LUT (L(n)) для n 4–8, m = 16, k = 8

120