книги / Практическая цифровая схемотехника

..pdf

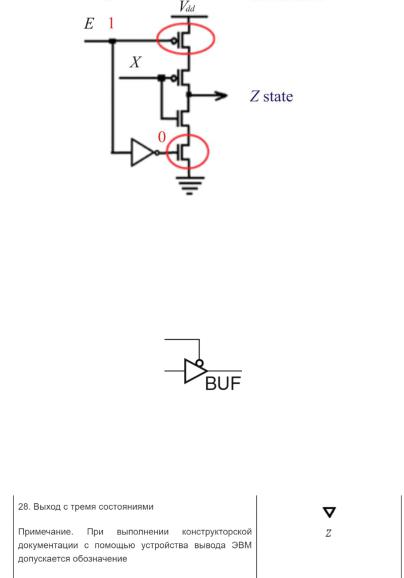

Рис. 23. Элемент с тремя состояниями на выходе,

Е = 1, на выходе Z-состояние, ток практически не течет

Буферный элемент, тристабильный элемент (3-State Buffer), был изобретен в середине 60-х годов ХХ века и изображается «по-английски» следующим образом (рис. 24).

Рис. 24. Тристабильный буфер

(3-state buffers, BUFT)

Обозначение по ГОСТ приведено на рис. 25.

Рис. 25. Обозначение выхода с третьим состоянием по ГОСТ

21

Элементы с тремя состояниями на выходе широко применяются в так называемых шинных формирователях для передачи информации по двунаправленным шинам (магистралям), что уменьшает число проводников на печатной плате.

12. ОДНОВЕНТИЛЬНЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА

Классификация интегральных микросхем дана в ГОСТ 17021-88 [10]. Цифровая интегральная микросхема – интегральная микросхема, предназначенная для преобразования и обработки сигналов, изменяющихся по закону дискретной функции [10]. Малая интегральная схема (МИС) – интегральная микросхема, содержащая до 100 элементов и (или) компонентов включительно [10]. Средняя интегральная схема (СИС) – интегральная микросхема, содержащая свыше 100 до 1000 элементов и (или) компонентов для цифровых интегральных микросхем и свыше 100 до 500 – для аналоговых интегральных микросхем [10]. Большая интегральная схема (БИС) – интегральная микросхема, содержащая свыше 1000 элементов и (или) компонентов для цифровых интегральных микросхем и свыше 500 для аналоговых интегральных микросхем [10]. Сверхбольшая интегральная схема (СБИС) – интегральная микросхема, содержащая свыше 100 000 элементов и (или) компонентов для цифровых интегральных микросхем с регулярной структурой построения, свыше 50 000 – для цифровых интегральных микросхем с нерегулярной структурой построения и свыше 10 000 – для аналоговых интегральных микросхем [10]. Прошло более 30 лет, и эта классификация в чем-то уже устарела (имеются микросхемы ПЛИС с десятками миллиардов транзисторов). Тем не менее мы говорим и о МИС, и о СИС, а все остальное – БИС, хотя одно время использовались и СБИС, и ультра СБИС, и др.

В далекие времена, когда малая (МИС) и средняя степень интеграции (СИС) микросхем преобладали, разработчики стре-

22

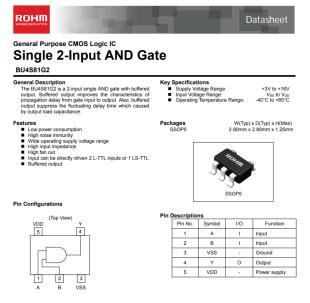

мились уместить в корпусе как можно больше устройств. Теперь, в эпоху больших и сверхбольших интегральных схем, появились Single Gate Logic Devices (одновентильные логические устройства), они занимают сейчас нишу реализации одиночных логических функций, преобразования уровня сигнала, буферизации линий интерфейса [21]. Пример приведен на рис. 26.

Рис. 26. Пример Single Gate Logic Devices –

один КМОП элемент И в корпусе

13. КОМБИНАЦИОННЫЙ АВТОМАТ, КОМБИНАЦИОННАЯ

ЛОГИКА НА ТРАНЗИСТОРНОМ УРОВНЕ

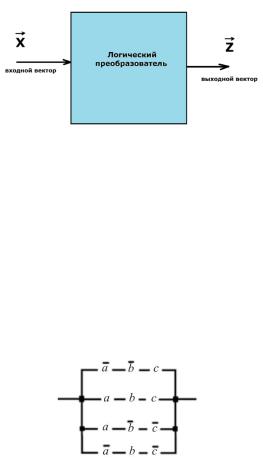

Комбинационная логика (Throughput Logic) некоторому входному набору (вектору) Х ставит в однозначное соответствие выходной набор (вектор) Z (рис. 27).

23

Рис. 27. Комбинационная логика

Такое устройство можно реализовать на логических элементах МИС, а можно разработать «собственный» элемент, то есть решить задачу на уровне транзисторов. Рассмотрим полный одноразрядный сумматор. Сумма сложения по модулю два (это СДНФ, и она не минимизируется) имеет вид:

|

|

|

|

|

|

|

|

|

|

s(abc) abc abc abc abc. |

(1) |

||||||||

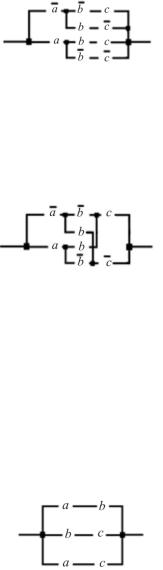

Получаем 12 транзисторов – по одному на каждую буковку (рис. 28).

Рис. 28. Реализация суммы по модулю два по СДНФ

Схемы, подобные приведенной на рис. 26, – пример так называемой PTL (Pass Transistor Logic – логика на передающих транзисторах). Для экономии транзисторов получим скобочную форму:

|

|

|

|

|

|

|

|

|

|

s(abc) a(bc bc) a(bc bc). |

(2) |

||||||||

24

Получаем 10 транзисторов (рис. 29).

Рис. 29. Реализация суммы по модулю два по скобочной форме

Еще больший эффект дает объединение цепей (использование того факта, что всегда есть либо цепь b, либо не b)

(рис. 30).

Рис. 30. Объединение цепей b и не b

Получаем 8 транзисторов. Очевидно, что эта функция самодвойственна, поэтому КМОП подсхема транзисторов другой проводимости так же будет иметь сложность 8. Итого 16. Рассмотрим вторую функцию сумматора – функцию переноса или мажоритарную (уже минимизированную в ДНФ):

p(abc) ab ac bc. |

(3) |

Соответствующая схема содержит 6 |

транзисторов |

(рис. 31). |

|

Рис. 31. Схема мажоритарной функции в ДНФ

25

Получим скобочную форму:

p(abc) a(b c) bc. |

(4) |

Для скобочной формы и для мостикового варианта получаем 5 транзисторов (рис. 32).

а |

б |

Рис. 32. Схема мажоритарной функции:

а– по скобочной форме; б – мостиковая

ВКМОП схеме мажоритарной функции будет 10 транзисторов. Итого весь сумматор 10+16=26 транзисторов. Но на самом деле мы не учли необходимости получения инверсий сигнала, это еще 3 инвертора, то есть 6 транзисторов для суммы. К тому же пока непонятно, как реализовать мажоритарную функцию, ибо при любых двух единицах на выходе схем (см. рис. 32) должна быть единица, но для протекания тока от источника питания на транзисторах должны быть нули. Хорошо, возьмем мажоритарную функцию инверсную, легко видеть, что она тоже самодвойственна и имеет вид

|

|

|

|

|

|

|

|

|

|

|

p(abc) a(b c) bc. |

(5) |

|||||||||

Тогда получим схему (рис. 33).

Рис. 33. Схема мажоритарной функции с инверсией

26

Очевидно, что нижняя КМОП подсхема будет иметь вид, приведенный на рис. 32, а. Тогда надо и функцию суммы брать инверсную. Но все равно получим те же неинверсные переменные, что и в выражении (1):

|

|

|

|

|

|

|

|

|

|

|

s(abc) abc abc abc abc. |

(6) |

|||||||||

Что делать? Оказывается можно применить гениальный ход – выразить функцию суммы через функцию переноса! Взглянем на таблицу истинности сумматора (рис. 34).

Рис. 34. Таблица истинности полного сумматора

Преобразуем таблицу истинности, сумму выразим через входные переменные+перенос (рис. 35).

Рис. 35. Преобразованная таблица истинности полного сумматора

27

Получим символическую форму суммы:

Sum(abcincout ) 2, 4,8,15 [0, 7,11,13]. |

(7) |

Выполняем минимизацию по карте Карно (рис. 36):

Рис. 36. Карта Карно для преобразованной функции суммы

Получаем:

|

|

|

|

Sum (a b cin )cout abcin . |

(8) |

||

Однако, такая функция (8) все равно неудобна для КМОП реализации в силу того, что всего одна переменная инверсна. Для инверсии суммы Sum’ получим:

Sum '(abcincout ) 0, 7,11,13 [2, 4, 8, 15]. |

(9) |

Минимизируем инверсию суммы по нулевым |

наборам |

(рис. 37). |

|

Рис. 37. Минимизация инверсии преобразованной суммы

28

Получаем:

|

|

|

|

|

|

|

|

|

|

|

Sum (a b cin )cout abcin . |

(10) |

|||||||||

Ввыражении (10) всего одна переменная не инверсна!

Сучетом того, что транзистор открывается нулем, получим то, что нужно:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sum (a b cin )cout abcin . |

(11) |

||||||||||||||||||||

А инверсию мажоритарной функции – выходного перено- |

||||||||||||||||||||||

са, мы уже получали: |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

cout (abcin ) ab acin bcin |

(12) |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a(b cin ) bcin . |

|

|||||||||||||||||||

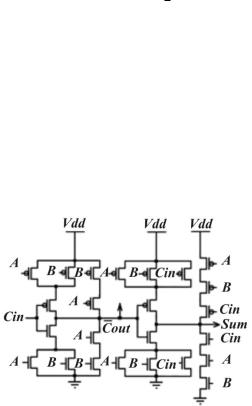

Получаем так называемый «зеркальный» |

сумматор |

|||||||||||||||||||||

(A Conventional Mirror Adder), видимо, потому, что все функ-

ции – инверсные, в его составе 24 транзистора (рис. 38).

Рис. 38. «Зеркальный» сумматор с преобразованной функцией суммы и инверсным переносом

Инверсия переноса также является выходом схемы, как и инверсия суммы. Итак, 24 транзистора. Но это на один разряд, а

29

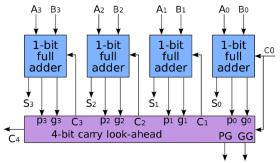

таких разрядов требуется сейчас уже 64. При этом в самом худшем случае перенос распространяется по цепочке из 64 одноразрядных сумматоров, что снижает быстродействие – надо долго ждать! Поэтому применяют специальные схемы ускоренного переноса (СУП, Carry look-ahead), в которой процесс переноса происходит параллельно с побитным суммированием (рис. 39).

Рис. 39. Четырехразрядный сумматор со схемой ускоренного переноса

14.ЗАДАНИЕ КОМБИНАЦИОННОГО УСТРОЙСТВА

ВВИДЕ ПРОГРАММЫ ЯЗЫКА VHDL

Большие схемы трудно представить в виде рисунка (графически), поэтому с 80-х годов ХХ века используют представление схем в виде текстов на специальных языках программирования, например, VHDL (Very high speed integrated circuits Hardware Description Language) [1, 4–7, 12]. Рассмотрим примеры.

CSA (conditional signal assignment) – табличное задание логической функции (3 переменных), например функции № 232, мажоритарной функции:

30