Министерство науки и высшего образования РФ

Федеральное государственное автономное образовательное учреждение высшего образования

«Омский государственный технический университет»

Кафедра «Информатика и вычислительная техника»

ОТЧЁТ ПО РАСЧЕТНО-ГРАФИЧЕСКОЙ РАБОТЕ

по дисциплине «Арифметические и логические основы вычислительной техники»

«Разработка арифметико-логического устройства, выполняющего деление со сдвигом сумматора без восстановления остатка в прямом коде»

студента Симон Карины Владимировны группы ПИН-221

Пояснительная записка

Шифр работы От-2068998-43-ПИН-221-37 ПЗ

Направление 09.03.04

Доцент, к.т. Н Червенчук И.В

Студент Симон К.В

Омск 2023

Реализация операции деления со сдвигом сумматора

без восстановления остатка

При выполнения операции

С=А В

мантисса mА загружается

в сумматор SM, мантисса mВ

загружается в регистр RM2,

регистр RM1 и сумматор

порядков SP обнуляются, в

счетчик загружается число порядков

мантиссы уменьшенное на один – CT=n-1.

При выполнении операции деления порядки

операндов должны вычитаться - СP=pA-pB.

В

мантисса mА загружается

в сумматор SM, мантисса mВ

загружается в регистр RM2,

регистр RM1 и сумматор

порядков SP обнуляются, в

счетчик загружается число порядков

мантиссы уменьшенное на один – CT=n-1.

При выполнении операции деления порядки

операндов должны вычитаться - СP=pA-pB.

Метод деление без восстановления остатка заключается в необходимости анализа старшего разряда сумматора (знака), на основе этого анализа решается какое действие необходимо делать на следующей итерации цикла.

Реализация деления:

1) Анализируется старший разряд сумматора(знак) SM.

Если старший разряд (знак) сумматора до сдвига равен 0 SM[1]=0 , то в следующей итерации цикла производится вычитание SM=SM-RM2,

Если старший разряд(знак) сумматора да сдвига равен 1 SM[1]=1, то в следующей итерации цикле производится сложение SM=SM-RM2

2) Выполняется сдвиг сумматора SM в сторону старших разрядов.

3) Производится действие на основе анализа 1 пункта.

4) Анализируется значение старшего разряда (знака) сумматора SM[1]

Регистр RM1 сдвигается в сторону старших разрядов и со стороны младших разрядов в RM1 задвигается инвертированное значение старшего разряда сумматора(знака).

5) Содержимое счетчика уменьшается на 1 СT=СТ-1, до тех пор пока СТ не равен 0.

По окончанию указанных действий на регистре RM1 должен находиться результат.

Схемы Алгоритма

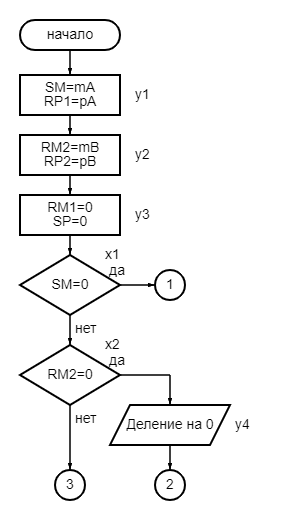

На рисунке 1 представлен алгоритм ввода данных и начальная проверка на возможность деления и в случае, если проверка подтверждается, осуществляется переход на вывод результата (в регистрах RM1 и SP находятся нулевые значения, они и выведутся.) Далее проверяется RM2 на ноль, если проверка подтверждается, выводится сообщение об ошибке «деление на ноль».

Рисунок 1- Схема алгоритма ввода данных и начальной проверки

На рисунке 2 представлена схема алгоритма работы с порядками. При выполнении операции деления в формате с плавающей запятой порядок результата находится как рС = рА – рВ, но если порядки представлены в прямом коде данное действие разворачивается в большой алгоритм.

Рисунок 2- Схема алгоритма работы с порядками

На рисунке 3 представлена схема алгоритма денормализации делимого.

Рисунок 3 – Схема алгоритма денормализации делимого

На рисунке 4 представлена схема алгоритма деления мантисс, представленных в прямом годе без восстановления остатка со сдвигом сумматора.

Рисунок 4- Схема алгоритма деления мантисс без восстановления остатка, со сдвигом сумматора

Схема устройства

На рисунке 5 представлена схема устройства деления со сдвигом сумматора, без восстановления остатка.

В таблице 1 представлены логические условия формируемые устройством.

В таблице 2 представлены управляющие сигналы, формируемые устройством.

Таблица 1.

Логические условия

Обозначение |

Сокращенная запись |

Комментарии |

X1 |

SM=0 |

Проверка сумматора мантисс (делимого) на ноль |

X2 |

RM2=0 |

Проверка регистра делителя на ноль |

X3 |

RP1[1] |

Знак порядка делимого |

X4 |

RP2[1] |

Знак порядка делителя |

X5 |

SP[1] |

Знак сумматора порядка |

X6 |

SM[1] |

Знак сумматора мантисс |

X7 |

CT=0 |

Проверка счетчика на ноль |

X8 |

SP[2…p] |

Проверка сумматора порядков на ноль (без учета знакового разряда) |

Таблица 2

Управляющие сигналы

Обозначение |

Сокращенная запись |

Комментарии |

y1 |

SM = mA, RP1 = pA |

Загрузка Мантиссы И Порядка А |

y2 |

RM2 = mB, RP2 = pB |

Загрузка Мантиссы И Порядка B |

y3 |

RM1 = 0, SP = 0 |

Сброс RM1 И SP |

y4 |

Деление на 0 |

Вывод Сигнала «Деление На 0» |

y5 |

SP = RP1 |

Загрузка Сумматора SP Из RP1 |

y6 |

SP = SP – RP2 |

Вычитание SP И RP2, Результат В SP (Содержимое RP2 Не Меняется) |

y7 |

SP = RP2 |

Загрузка Сумматора SP Из RP2 |

Обозначение |

Сокращенная запись |

Комментарии |

y8 |

SP = SP – RP1 |

Вычитание SP И RP1, Результат В SP (Содержимое RP1 Не Меняется) |

y9 |

SP[1] = 1 |

Установка Знакового Разряда SP |

y10 |

RP2[1] = 0 |

Сброс Знакового Разряда RP2 |

y11 |

SP = SP + RP2 |

Сумма SP И RP2, Результат В SP (Содержимое RP2 Не Меняется) |

y12 |

RP1[1] = 0 |

Сброс Знакового Разряда RP1 |

y13 |

Переполнение – |

Вывод Сигнала «Переполнение –» |

y14 |

T = SM[1] ⊕ RM2[1] |

Получение Знака Результата И Сохранение Его В Триггере |

y15 |

SM[1] = 0, RM2[1] = 0 |

Сброс Знаковых Разрядов SM И RM2 |

y16 |

SM = SM-RM2 |

Вычитание SM И RМ2, Результат В SМ |

y17 |

SM← |

Сдвиг SM Влево |

y18 |

SP = SP+1 |

Увеличение SP На 1 |

y19 |

SP = SP-1 |

Уменьшение SP На 1 |

y20 |

SP[1] = 0 |

Сброс Знакового Разряда SP |

y21 |

CT = n-1 |

Загрузка Счетчика (N-1 Циклов) |

y23 |

SM = SM+RM1 |

Сложение SM И RМ2, Результат В SМ |

y24 |

ci = SM[1], RM1← |

В RM1 Задвигается Очередной Разряд Частного C |

y25 |

RM1[1] = T |

Присвоение Знака Результата |

y26 |

Вывод RM1, SP |

Вывод Мантиссы И Порядка Результата |

y27 |

Переполнение + |

Вывод Сигнала «Переполнение +» |

y28 |

SM→ |

Сдвиг SM вправо |