670_Maglitskij_B.N._Otsenka_vlijanija_iskazhenij_i_pomekh_

.pdf

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

4 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

5 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

6 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

7 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

8 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

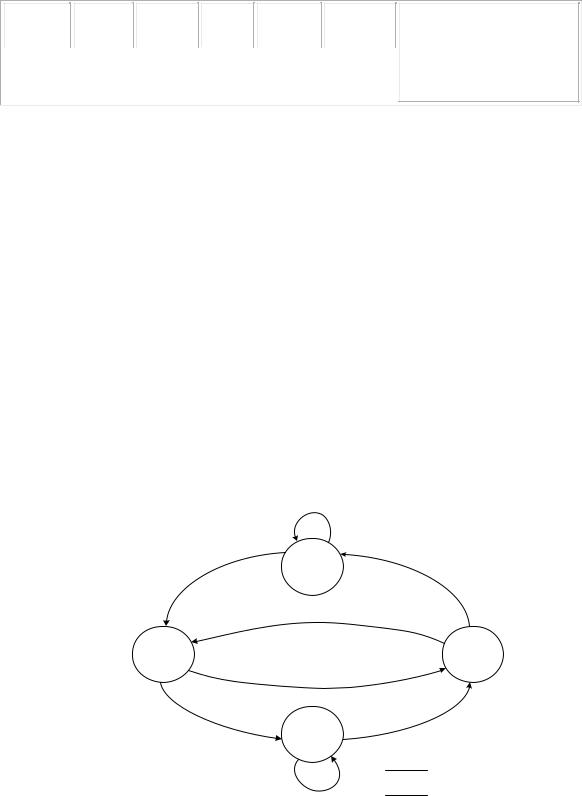

Рисунок 1.22. – Побайтовое обнаружение и исправление одиночной ошибки в блочном кодере

При наличии одиночной ошибки в этой 8 8 64 - битовой матрице можно указать не только строку, содержащую ошибку, но и столбец с ошибкой, а значит - ошибочный бит, лежащий на пересечении строки и столбца (например, если обнаружена ошибка в 4 – й строке (1 в 8 столбце), 8 – байтовой последовательности, а также в 4 – столбце (1 в 8 строке), то, таким образом, обнаружен ошибочный бит в 4 – й строке 4 – го столбца матрицы).

ВАЖНО! Таким образом, матрица рисунка 4.8 позволяет при ее реализации в виде систематических байтовых кодеров обнаружить и исправить одиночные ошибки.

Однако, кратные ошибки этой схемой исправить невозможно. Для коррекции кратных ошибок применяются более совершенные и сложные схемы блочных кодеров.

Примером блочного кода, наиболее часто используемого на практике является код Рида – Соломона (RS).

31

Коды Рида-Соломона (Reed-Solomon codes – RS codes) – это широко используемый подкласс недвоичных кодов БХЧ. При использовании кодов Рида - Соломона данные обрабатываются порциями по m бит, именуемыми символами. Код (n, k) характеризуется следующими параметрами:

Длина символа |

m бит |

Длина блока |

n = (2m – 1) символов = m(2m – 1) бит |

Длина блока данных |

k символов |

Размер контрольного кода |

n - k = 2t символов = m(2t) бит |

Минимальное расстояние |

dmin = (2t + 1) символов |

Таким образом, алгоритм кодирования расширяет блок k символов до размера n, добавляя (n-k) избыточных контрольных символов.

Как правило, m является степенью 2; широко используется значение т = 8.

Рассмотрим пример. Пусть t =1, т = 2. Обозначая символы как 0, 1, 2, 3, их двоичные эквиваленты можно записать как 0 = 00; 1 = 01; 2 = 10; 3 = 11. Код имеет следующие параметры:

n = 22 – 1 = 3 символа = 6 бит, n - k = 2 символа = 4 бит.

С помощью данного кода можно исправить любой пакет ошибок, который искажает 2-битовый символ.

Коды Рида-Соломона удобны для исправления пакетов ошибок. Данный тип кодов характеризуется высокоэффективным использованием избыточности. Длина блоков и размеры символов могут легко приспосабливаться под сообщения разных размеров. Кроме того, для таких кодов существуют эффективные методы декодирования [4].

1.3.5. Сверточные коды

В отличие от блочных кодов, сверточные коды являются непрерывными

(рекуррентными). Их кодирование и декодирование осуществляется непрерывно, без деления информационной последовательности на блоки.

Сверточные коды являются частным случаем непрерывных (рекуррентных) кодов. В основу их построения положен принцип формирования проверочных разрядов путем суммирования по модулю 2 каждого информационного разряда с некоторым набором предыдущих разрядов. Пример простейшего сверточного кодера приведен на рисунке 1.23.

32

|

+ |

|

|

Входная |

|

Выходное |

|

информационная |

1 |

||

кодовое слово |

|||

последовательность |

|||

|

|||

|

|

||

|

2 |

К |

|

|

|

+

Рисунок 1.23. – Пример схемы сверточного кодера

На рисунке 1.23 изображен сверточный кодер (2,1) с длиной кодового ограничения К=3. В нем имеется n = 2 сумматоров по модулю 2, следовательно, скорость кодирования кода к/n=1/2. При каждом поступлении бит помещается в крайний левый разряд регистра, а записанные биты смещаются на одну позицию вправо. Считывание выходных символов коммутатором К осуществляется после поступления каждого информационного символа, в результате чего формируются пары кодовых символов, образующих кодовое слово, связанное с поступившим битом.

Выбор связи между сумматорами и разрядами регистра влияет на характеристики кода.

Рассмотрим работу кодера при поступлении на его вход информационной последовательности 101. Предположим, что к моменту поступления кодовой последовательности все ячейки регистра находились в состоянии «0» (таблица 1.1)

Таблица 1.1 – Последовательность работы кодера

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Содержимое ячеек |

|

Выходное ко- |

Примечание |

|

||||||

|

п/п |

|

|

|

|

|

|

|

довое слово |

|

|

||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

1 |

|

2 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Исходное состояние |

|

|

1 |

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

2 |

|

1 |

|

0 |

|

0 |

|

1 |

|

1 |

Ввод в регистр 101 |

|

|

|

|

|

|

|

|

|

|

|||||

|

3 |

|

0 |

|

0 |

|

0 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

4 |

|

1 |

|

1 |

|

1 |

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

|

Ввод в регистр 00

5 |

|

0 |

|

0 |

|

0 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

Для очистки регистра после введения трех информационных бит введены (К-1) = 2 нуля. Таким образом, последовательность на выходе кодера выглядит следующим образом: 1110001011. Для удаления сообщения из кодера требуется на 1 меньше нулей, чем число разрядов в регистре, или К-1 очищенных бит.

Отметим, что в рассмотренном примере при входной последовательности из 3 бит и выходной последовательности из 10 бит эффективная степень кодирования составляет к/n = 0,3, что значительно меньше величины 0,5, которую можно было бы ожидать, зная, что каждый бит данных на входе порождает пару канальных битов на выходе. Причина этого заключается в том, что финальные биты данных нужно провести через кодер. Все канальные биты на выходе требуются в процессе декодирования. Если бы сообщение было длинное, например 300 бит и значение степени кодирования 300/640 было бы значительно ближе к 0,5.

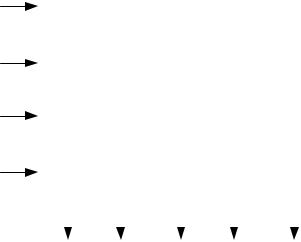

Одним из способов представления простых кодирующих устройств является диаграмма состояний. Такое представление кодера приведено на рисунке

1.24.

|

00 |

|

11 |

a=00 |

11 |

|

||

|

|

|

|

00 |

|

b=10 |

|

c=01 |

|

10 |

|

01 |

d=11 |

01 |

|

|

|

|

|

Входной бит 0 |

|

10 |

Входной бит 1 |

|

|

Рисунок 1.24. – Диаграмма состояний кодера (степень кодирования ½, К=3)

Пути между состояниями – кодовые слова ветвей на выходе, являющиеся результатом переходов между состояниями. Состояния регистра выбраны следующими: а = 00, b = 10, c = 01, d = 11.

34

Существует всего два исходящих из каждого состояния перехода, соответствующие двум возможным входным битам. Для каждого пути между состояниями записано кодовое слово на выходе, связанное с переходами между состояниями. При изображении путей сплошной линией принято изображать путь, связанный с нулевым входным битом, а пунктирной линией – пути, связанные с единичным входным битом.

ВАЖНО! Отметим, что за один переход невозможно перейти из данного состояния в любое произвольное. Так как за единицу времени перемещается только один бит, существует только два возможных перехода между состояниями, в которые регистр может переходить за время прохождения каждого бита. Например, если состояние кодера 00, то при следующем смещении возможно возникновения состояний 00 или 10.

Несмотря на то, что диаграммы состояний полностью описывают кодер, по сути, их нельзя использовать для легкого отслеживания переходов кодера в зависимости от времени, так как диаграмма не представляет динамики изменений.

Древовидная диаграмма прибавляет к диаграмме состояний временное измерение. Древовидная диаграмма сверточного кодера приведена на рисунке

1.25.

В каждый последующий момент прохождения входного бита процедура кодирования может быть описана с помощью перемещения по диаграмме слева направо, причем каждая ветвь дерева описывает кодовое слово на выходе. Правило ветвления для нахождения кодовых слов следующее: если входным битом является нуль, то он связывается со словом, которое находится путем перемещения в следующую (по направлению вниз) правую ветвь. Предполагается, что первоначально кодер содержал одни нули. Диаграмма показывает, что если первым битом был 0, то кодовым словом ветви на выходе будет 00, а если первым входным битом была единица, то кодовым словом на выходе будет 11 и т.д.

35

|

|

|

|

|

|

|

|

|

00 |

а |

00 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

00 |

а |

|

|

11 |

||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

11 |

b |

10 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

00 |

а |

|

01 |

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

10 |

c |

11 |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

00 |

|||

|

|

|

|

|

|

|

|

11 |

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

01 |

d |

01 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

00 |

а |

|

|

|

|

10 |

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

11 |

a |

00 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

11 |

|||

|

|

|

|

|

|

10 |

c |

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

00 |

b |

10 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

11 |

b |

|

01 |

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

01 |

c |

11 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

00 |

|||

0 |

|

а |

|

|

|

|

|

01 |

d |

|

|

|

|

|

|

|

|

|

|

|

10 |

d |

01 |

||

|

|

|

|

|

|

|

|

|||||

1 |

|

|

|

|

|

|

|

|

|

10 |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

00 |

a |

00 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

11 |

|||

|

|

|

|

|

|

11 |

a |

|

|

|||

|

|

|

|

10 |

c |

|

|

11 |

b |

10 |

||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

01 |

|||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

10 |

c |

11 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

00 |

|||

|

|

|

|

|

|

|

|

00 |

b |

|

|

|

|

|

|

11 |

b |

|

|

|

|

|

01 |

d |

01 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

10 |

|||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

11 |

a |

00 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

11 |

|||

|

|

|

|

|

|

01 |

c |

|

|

|||

|

|

|

|

|

01 |

d |

|

|

|

00 |

b |

10 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

01 |

|||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

01 |

c |

11 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

10 |

d |

|

|

00 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

10 |

d |

01 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

10 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 1.25. – Древовидное представление кодера

Например, входная последовательность 11011 представляется жирной линией на древовидной диаграмме. Этот путь соответствует входной последовательности 1101010001.

Отметим, что при описании с помощью древовидной диаграммы последовательности произвольной длины возникают проблемы, связанные с ростом числа ответвлений.

Исследование древовидной диаграммы показывает, что в этом примере после третьего ветвления структура повторяется. В общем случае древовидная структура повторяется после К ответвлений, где К – длина кодового ограничения. Решетчатая диаграмма, которая использует повторяющуюся структуру, дает более удобное описание кодера.

ВАЖНО! Декодировние сверточных кодов производится по достаточно сложным алгоритмам, наиболее известным из которых является алгоритм декодирования Витерби [3].

36

1.3.6. Перемежение

Перемежение представляет собой такое изменение порядка следования символов информационной последовательности, при котором стоящие рядом символы оказываются разделенными несколькими другими символами. Такая процедура предпринимается с целью преобразования групповых ошибок (пакетов ошибок) в одиночные ошибки, с которыми легче бороться с помощью блочного и сверточного кодирования. Использование перемежения - одна из характерных особенностей сотовой связи, и это является следствием неизбежных глубоких замираний сигнала в условиях многолучевого распространения, которое всегда имеет место, особенно в условиях плотной городской застройки. При этом группа следующих один за другим символов, попадающих на интервал замирания (провала сигнала), с большой вероятностью оказывается ошибочной. Если же перед выдачей информационной последовательности в радиоканал она подвергается процедуре перемежения, а на приемном конце восстанавливается прежний порядок следования символов, то пакеты ошибок с большой вероятностью рассыпаются на одиночные ошибки.

Известно несколько различных схем перемежения: диагональная, блочная, сверточная и др. Рассмотрим принцип блочного перемежения, применяемого в стандарте IS-95.

В случае блочного перемежения входная информация делится на блоки, по n субблоков (или символов) в каждом, и в выходной последовательности чередуются субблоки k последовательных блоков. Работу этой схемы можно представить в виде записи блоков входной последовательности в качестве строк матрицы размерности k n (рисунок 1.26), считывание информации на которой производится по столбцам ошибок.

Вход

а1 |

а2 |

а3 |

….. |

an |

|||||

|

|

|

|

|

|

|

|

|

|

b1 |

b2 |

b3 |

….. |

bn |

|||||

|

|

|

|

|

|

|

|

|

|

..… |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

к1 |

к2 |

к3 |

…... |

кn |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выход

Рисунок 1.26. – Схема блочного перемежения

37

Следовательно, если входная последовательность в этом примере имела

вид: а1, а2 ,.....аn, в1, в2,....вn ,к1, к2,...кn, то выходная будет такой: а1, в1, к1, а2, в2,

к2, аn, вn, кn. Субблоки, или символы в частном случае могут состоять лишь из одного бита. Схема блочного перемежения вносит большую задержку, чем схема диагонального перемежения, но значительно сильнее рассосредотачивает символы группы ошибок.

1.3.7. Скремблирование цифровых потоков

Вцифровых системах радиосвязи при определенных статистических свойствах цифрового сигнала ухудшается качество передачи информации. Так, например, при наличии в цифровом сигнале периодических комбинаций символов нарушается работа канала цикловой синхронизации. Кроме того, в упомянутых ситуациях изменяется характер спектра модулированного сигнала, что ухудшает условия ЭМС радиосредств.

Например, при ВFSK при равновероятных двоичных символах энергия сигнала сосредоточена в широкой полосе частот. В упомянутых выше ситуациях энергия излучаемого сигнала сосредотачивается в узкой полосе частот.

Кроме того, в таких ситуациях ухудшается качество работы канала тактовой синхронизации в регенераторах, что приводит к ошибкам в принятии решений и появлению достаточно длинного пакета ошибок в сигнале на стороне приема.

Всвязи с этим цифровой сигнал подвергается специальному кодированию, направленному на разрушение регулярных связей в последовательности символов цифрового сигнала. Такое преобразование называется скремблированием.

Отметим, что в современных цифровых системах радиосвязи скремблирование используется почти всегда, независимо от метода разделения каналов. Оно оказывается полезным по ряду причин и, в частности, разрушает регулярные структуры.

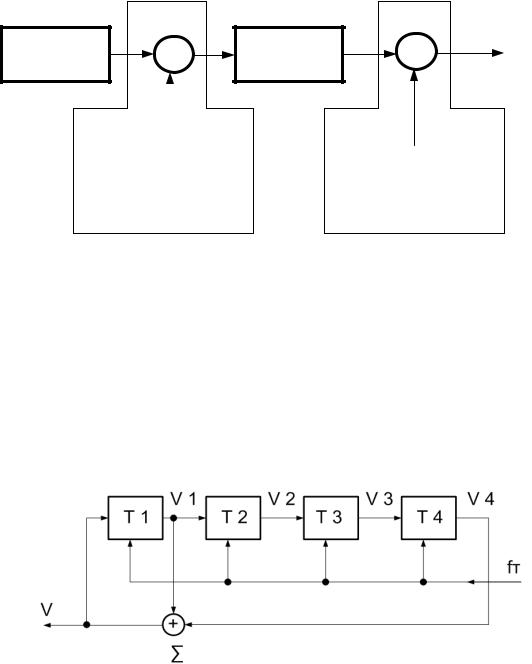

Наиболее эффективный вариант скремблирования связан с формированием специальной цифровой псевдослучайной последовательности (ПСП). Для скремблирования формируют ПСП, синхронную с цифровым сигналом и с периодом, равным в простейшем случае единице, а в более общем случае – несколько циклов данного сигнала. Сформированная таким образом ПСП складывается по модулю 2 с цифровым сигналом (синхрогруппы преобразованию не подвергаются). Далее сформированный сигнал передается по каналу связи (ри-

сунок 1.27).

На приемной стороне производится обратное преобразование – дескремблирование. После того, как в системе связи будет установлен цикловый синхронизм, в дескремблере формируется та же ПСП, что и на передаче, и с ее помощью вновь осуществляется скремблирование цифрового сигнала. При правильной фазировке ПСП повторное скремблирование означает дескремблирование, поскольку двукратное добавление по mod 2 и той же последовательно-

38

сти эквивалентно добавлению ко всем символам цифрового сигнала нуля, т.е. его неискаженному восстановлению.

ЦС |

+ |

Канал |

+ |

ЦС |

|

|

|

|

|

|

ПСП |

|

ПСП |

|

|

|

|

|

|

|

|

|

Скремблер |

|

Дескремблер |

|

Рисунок 1.27. – Структурная схема скремблирования цифрового сигнала

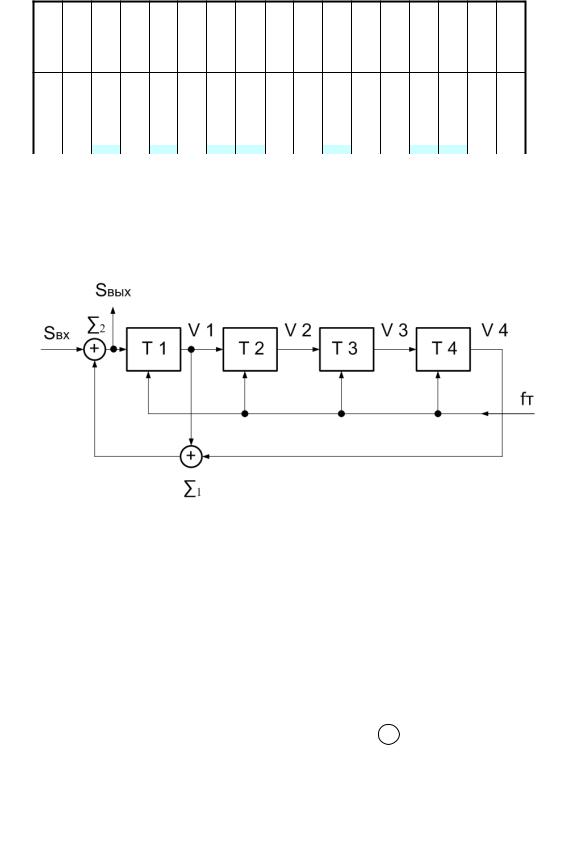

Обычно генераторы ПСП строятся на базе последовательных регистров сдвига. На рисунке 1.28 показан вариант 4-х разрядного регистра сдвига с обратными связями (Т – ячейка памяти, fт – сигнал тактовой частоты). Состояния

ячеек памяти и состояние выхода регистра обозначены как V. Процесс5.2формирования.2 ПоследовательныйПСП поясняетсярегистртаблицейсдвиганном1.2. В случае

формируется ПСП длиной М = (2N – 1) = 15, где N – число разрядов регистра сдвига. Структура скремблера показана на рисунке 1.29.

Рисунок 1.28. – Пример генератора ПСП

05.04.2013 16:43 |

С и РРСП (лекции |

5 |

|

Б.Н.Маглицкого) |

|

39

Процесс формирования ПСП

Таблица 1.2 – Формирование ПСП

Так- |

1 |

2 3 |

4 5 |

6 |

7 8 9 |

10 |

11 12 |

13 |

14 14 |

16 |

ты |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V2 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V3 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

V4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

5.2.3 |

Структурная |

схема |

|

скремблера |

|

|

||||||||

V |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 1.29. – Структурная схема скремблера

05.04.2013 16:43 С и РРСП (лекции 7

Выходной сигнал скремблераБ:.Н.Маглицскремблераого)

Выходной сигнал

V4(t)= V3(t-T)=V2(t-2T)=V3(t-3T)

Т псп = 2^n - 1

Выходной сигнал: V(t) = V1(t) + V4(t)

На рисунке 1.30. показана структурная схема дескремблера.

05.04.2013 16:44 |

С и РРСП (лекции |

8 |

|

Б.Н.Маглицкого) |

|

40