- •Введение

- •1. Производство Интегральных Схем на современном этапе

- •2. Основы технологии производства Интегральных Схем

- •3. Библиотеки топологических элементов. Резисторы и конденсаторы

- •4. Библиотеки топологических элементов. Моп-транзисторы

- •5. Библиотеки топологических элементов. Биполярные транзисторы

- •6. Понятие топологии. Цели и задачи топологического проектирования

- •7. Проектирование топологии аналоговых схем

- •8. Обзор коммерческих фабрик по производству Интегральных схем

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО

«Воронежский государственный технический университет»

Ю.С. Балашов А.В. Русанов

Проектирование топологии

аналоговых устройств сверхбольших

интегральных схем

Утверждено Редакционно-издательским советом

университета в качестве учебного пособия

Воронеж 2011

УДК 621.396.6

Балашов Ю.С. Проектирование топологии аналоговых устройств сверхбольших интегральных схем: учеб. пособие. / Ю.С. Балашов, А.В. Русанов. Воронеж: ФГБОУ ВПО «Воронежский государственный технический университет», 2011. 81 с.

В учебном пособии рассматривается проектирование топологии аналоговых устройств. Дано описание технологического процесса и его основные технологические операции, описание библиотек топологических элементов, а также основы проектирования топологии аналоговых блоков.

Издание соответствует требованиям Федерального государственного образовательного стандарта высшего профессионального образования по направлению 211000 «Конструирование и технология электронных средств», магистерской программе 211000.68 «Информационные технологии проектирования электронных средств, выполненных по субмикронной технологии»), дисциплине «Проектирование топологии аналоговых устройств сверхбольших интегральных схем». Учебное пособие также предназначено для слушателей профессиональной переподготовки специалистов (программа «Схемотехническое проектирование аналоговых устройств сверхбольших интегральных схем (СБИС) с топологическими нормами 90 нм»).

Издание предназначено для студентов очной формы обучения.

Учебное пособие подготовлено в электронном виде в текстовом редакторе Microsoft Word и содержится в файле Русанов Уч.пособ.doc.

Табл. 3. Ил. 38. Библиогр.: 5 назв.

Рецензенты: ОАО «Концерн Созвездие»

(директор Центра системного проектирования В.И. Конопкин);

канд. техн. наук, доц. Е.Д. Алперин

© Балашов Ю.С., Русанов А.В., 2011

© Оформление. ФГБОУ ВПО «Воронежский

государственный технический

университет», 2011

Введение

Целью учебной дисциплины «Проектирование топологии аналоговых устройств сверхбольших интегральных схем» является предоставление необходимого базиса знаний инженера-тополога. Учебный материал разделен на три тематических раздела. Первый содержит краткое описание технологического процесса и его основные технологические операции. Второй посвящен описанию библиотек топологических элементов. Основы проектирования топологии аналоговых блоков описаны в третьем разделе.

В результате изучения дисциплины слушатель должен знать основы проектирования топологии аналоговых интегральных схем с топологическими нормами 90 нм и приобрести практический опыт разработки топологии аналоговых устройств в современных САПР Cadence Virtuoso и Cadence Virtuoso XL.

1. Производство Интегральных Схем на современном этапе

Большинству разработчиков интегральных схем никогда не придется сталкиваться с деталями технологического процесса, лежащего в основе возникновения полупроводниковой революции. Тем не менее, некоторое понимание тех шагов, которые приводят к получению работающего кремниевого чипа, весьма полезно для того, чтобы почувствовать физический смысл ограничений, которых должен придерживаться разработчик, а также разобраться во взаимосвязи между процессом производства и такими параметрами, как, скажем, стоимость.

В данной лекции приводится краткое описание шагов и методик, использующихся в технологическом процессе изготовления современных интегральных схем.

Тут представлена общая картина последовательности и взаимодействия различных шагов процесса. Слушатель узнает, что именно набор оптических масок, или фотошаблонов, является основным интерфейсом между внутренними особенностями процесса изготовления и разработкой, которую пользователь хотел бы видеть воплощенной в виде кремниевой структуры. Эти маски определяют рисунки, которые, будучи перенесенными на различные слои полупроводникового материала, формируют элементы электронных приборов и электрические соединения. Как следствие, для получения полностью работоспособной схемы эти рисунки должны удовлетворять некоторым ограничениям по минимальной ширине и расстоянию между ними. Такой набор ограничений называется нормами проектирования и играет роль контракта между разработчиком интегральной схемы и технологом. Если разработчик придерживается этих правил, то он получает гарантию того, что схему можно изготовить.

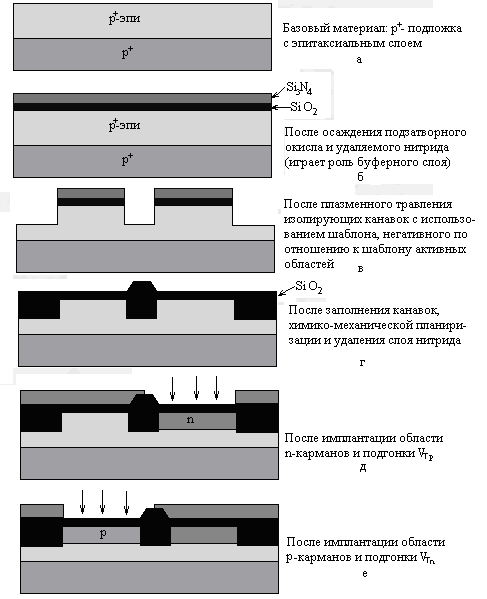

Схема упрощенного КМОП-процесса.

Укрупненная схема возможного процесса изготовления КМОП ИС приведена на рис. 1.1.

Рис. 1.1. Упрощенная последовательность этапов процесса

изготовления КМОП ИС по двухкарманной технологии

Процесс начинается с задания активных областей, т.е. областей, в которых будут формироваться транзисторы. Все остальные области кристалла микросхемы будут закрываться толстым слоем двуокиси кремния (Si02), называемым защитным окислом. Этот слой оксида играет роль изоляции между соседними приборами и либо выращивается, либо осаждается в вытравленные канавки, — отсюда и название: изоляция канавками. Дополнительная изоляция обеспечивается обратно смещенным np-диодом, образующимся в результате введения под защитный окисел дополнительной р+-области, называемой противоканалъной (или охранной) областью. На следующем этапе методом ионной имплантации формируются слаболегированные р- и n-карманы. Для формирования в р-кармане п-МОП-транзистора ионной имплантацией (или диффузией) в слаболегированной подложке р-типа формируются сильно легированные области истока и стока п-типа. Области стока и истока разделяются тонким слоем Si02, называемым подзатворным окислом, который сам закрывается проводящим поликристаллическим кремнием (или поликремнием). Проводящий материал образует затвор транзистора. МОП-транзисторы с каналом р-типа формируются аналогичным образом (только р- и п-области меняются местами). Для обеспечения электрических соединений между транзисторами поверх этих приборов осаждается несколько разделенных диэлектриком слоев металла (чаще всего это алюминий).

Более детальное разбиение технологического маршрута на операции обработки и результаты их влияния на полупроводниковый материал показаны на рис. 1.2.

Хотя в свете изложенного выше смысл большинства операций должен быть понятен из рисунка, относительно отдельных операций все же стоит дать небольшой комментарий. Процесс начинается с р-подложки, на поверхности которой сформирован слаболегированный эпитаксиальный р-слой (рис. 1.2, а). Затем осаждается тонкий слой Si02, который будет служить в качестве подзатвориого окисла, и поверх него осаждается удаляемый более толстый слой нитрида кремния (рис. 1.2, б).

Рис. 1.2 (а-е). Диаграмма процесса изготовления n-МОП

и p-МОП транзистора по двухкарманной КМОП-технологии

С использованием фотошаблона, рисунок на котором представляет собой негатив по отношению к рисунку активных областей, методом плазменного травления формируются канавки, изолирующие приборы друг от друга (рис. 1.2, в). После противоканальной имплантации канавки заполняются Si02 и выполняется ряд шагов для обеспечения плоскостности поверхности (включая подтравливание окисла с использованием шаблона-негатива слоя активных областей и химико-механическую планаризацию). В этот момент удаляется и вспомогательный слой нитрида (рис. 1.2, г).

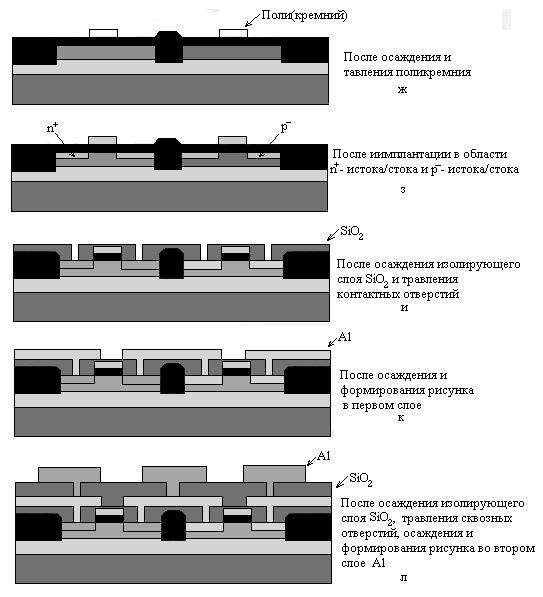

Рис. 1.2. (ж-л)

С использованием фотошаблона слоя n-карманов вскрываются области, соответствующие их расположению на кристалле (остальная часть поверхности остается закрытой буферным материалом), после чего выполняется последовательность операций имплантации и отжига, позволяющих получить заданный уровень легирования в кармане. Затем для подгонки величины порогового напряжения р-МОП-транзисторов выполняется вторая имплантация. В ходе данной имплантации изменяется уровень легирования только в той области, которая непосредственно примыкает к подзатворному диэлектрику (рис. 1.2, д). Аналогичные операции (только используется другая легирующая примесь) выполняются и для создания р-карманов и подгонки порогового напряжения n-МОП-транзисторов (рис. 1.2, е). После этого химически осаждается тонкий слой поликремния и с помощью фотошаблона слоя поликремния в нем создается рисунок. Поликремний используется как в качестве материала электрода затвора транзисторов, так и в качестве среды для создания межсоединений (рис. 1.2, ж).

Далее последовательно следуют операции ионной имплантации, в ходе которых легируются области истока и стока р-МОП-транзисторов (р+) и n-МОП-транзисторов (n+) соответственно (рис. 1.2, з), после завершения которых стравливается тонкий подзатворный окисел, незакрытый поликремнием. Эти же операции имплантации используются для легирования поверхности поликремния для уменьшения величины его удельного сопротивления. У нелегированиого поликремния удельное сопротивление очень высоко. Обратите внимание, что поликремниевый затвор, конфигурация которого формируется до легирования, фактически задает точное расположение области канала и, следовательно, расположение областей истока и стока. Такая процедура, называемая процессом самосовмещения, позволяет добиться очень точного позиционирования двух областей относительно затвора. Метод самосовмещения очень полезен в плане снижения паразитных емкостей транзистора. Процесс продолжается осаждением металлических слоев системы межсоединений. На этом этапе повторяется выполнение следующих операций (рис. 1.2, и-л): осаждение изолирующего материала (чаще всего это SiO2), травление контактных или сквозных отверстий, осаждение металла (чаще всего это алюминий и медь, хотя для нижних слоев часто применяется и вольфрам) и создание рисунка межсоединений. Промежуточные этапы планаризации с использованием химико-механической полировки обеспечивают достаточную плоскостность поверхности даже при наличии нескольких слоев межсоединений. После осаждения последнего слоя металла в целях защиты поверхность закрывается слоем пассивации или остпекловываетпся. Обычно это слой Si02, получаемый методом осаждения из паровой фазы, хотя часто еще добавляется слой нитрида кремния, поскольку он более влагонепроницаем. На последнем этапе вытравливаются окна к контактным площадкам, использующимся для термокомпрессионной приварки проволочных выводов.

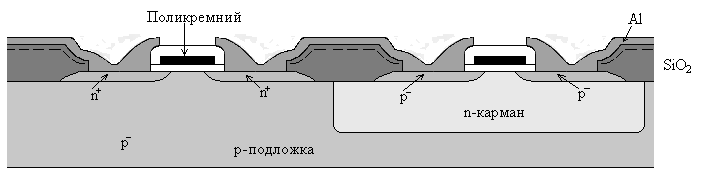

КМОП инвертор. На рис. 1.3 показан упрощенный вид поперечного сечения типового КМОП-инвертора.

Рис. 1.3. Поперечное сечение структуры, получаемой

в ходе КМОП-процесса

Процесс получения КМОП ИС требует формирования в объеме одной и той же пластины кремния как п-канальных (n-МОП), так и р-канальных (р-МОП) транзисторов. Чтобы иметь возможность размещения приборов обоих типов, необходимо создать специальные области, называемые карманами, тип полупроводникового материала в которых противоположен типу канала. МОП-транзистор с р-каналом должен создаваться либо в подложке n-типа, либо в п-кармане, тогда как n-МОП-транзистор размешается либо в подложке р-типа, либо в р-кармане. Поперечное сечение, показанное на рисунок3, соответствует КМОП-щюцессу с n-карманами, когда п-МОП-транзисторы формируются в подложке р-типа, а р-МОП-приборы размещаются в п-кармане. В современных процессах все чаще используется двухкармаппый подход, когда в эпитаксиалыю выращенном слое формируются как n-карманы, так и р-карманы (рис. 1.4).

КМОП-процесс требует большого количества шагов, каждый из которых состоит из последовательности базовых операций. В ходе процесса изготовления ряд этих шагов и/или операций часто периодически повторяется.

Рис. 1.4. Поперечное сечение современной КМОП-структуры,

получаемой по двухкарманной технологии