- •Методические указания

- •Лабораторная работа №1 проектирование запоминающей ячейки оперативного запоминающего устройства статического типа на языке vhdl

- •Лабораторная работа №2 проектирование дешифраторов адреса на языке vhdl

- •Лабораторная работа №3 проектирование матрицы запоминающих ячеек оперативного запоминающего устройства статического типа на языке vhdl

- •Лабораторная работа №4 проектирование структуры оперативного запоминающего устройства статического типа на языке vhdl

- •Указания по оформлению отчёта

- •Библиографический список

- •Содержание

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО

"Воронежский государственный технический университет"

Кафедра конструирования и производства радиоаппаратуры

Методические указания

к выполнению лабораторных работ № 1-4

по дисциплине «Специализированные БИС и устройства функциональной электроники в приборостроении»

для студентов направления 200100.62 «Приборостроение»

(профиль «Приборостроение») очной и заочной форм обучения

Воронеж 2013

Составитель канд. техн. наук А.А. Пирогов

УДК 621.396

Методические указания к выполнению лабораторных работ № 1-4 по дисциплине «Специализированные БИС и устройства функциональной электроники в приборостроении» для студентов направления 200100.62 «Приборостроение» (профиль «Приборостроение») очной и заочной форм обучения / ФГБОУ ВПО "Воронежский государственный технический университет"; cост. А.А. Пирогов. Воронеж, 2013. 23 с.

В работе изложены требования и рекомендации по подготовке и выполнению лабораторной работы № 1 «Проектирование запоминающей ячейки оперативного запоминающего устройства статического типа на языке VHDL», лабораторной работы № 2 «Проектирование дешифраторов адреса на языке VHDL», лабораторной работы № 3 «Проектирование матрицы запоминающих ячеек оперативного запоминающего устройства статического типа на языке VHDL» и лабораторной работы № 4 «Проектирование структуры оперативного запоминающего устройства статического типа на языке VHDL», по каждой работе приводятся краткие теоретические сведения, домашние и лабораторные задания с рекомендациями по их выполнению, контрольные вопросы и список рекомендуемой литературы.

Методические указания подготовлены в электронном виде и содержатся в файле «Методичка СБИС_1» doc.

Ил. 10. Библиогр.: 3 назв.

Рецензент канд. техн. наук, доц. М.А. Ромащенко

Ответственный за выпуск зав. кафедрой д-р техн. наук, проф. А.В. Муратов

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

© ФГБОУ ВПО "Воронежский государственный технический университет", 2013

Лабораторная работа №1 проектирование запоминающей ячейки оперативного запоминающего устройства статического типа на языке vhdl

1.1. Общие указания по выполнению лабораторной работы

Целью лабораторной работы является углубление и закрепление знаний студентов в области основных понятий цифровой схемотехники, моделей и параметров логических элементов, а также получение навыков в проектировании СБИС с использованием языка VHDL. Лабораторный практикум посвящен проектированию структуры СБИС оперативного запоминающего устройства (ОЗУ) статического типа. В рамках данной лабораторной работы необходимо построить модель запоминающей ячейки ОЗУ на языке описания аппаратных средств VHDL с использованием программного комплекса Active-HDL.

На выполнение лабораторной работы отводится восемь часов.

Перед выполнением лабораторной работы студент должен самостоятельно выполнить домашнее задание в соответствии с данными методическими указаниями.

Студент, явившийся на занятия, должен иметь методические указания по данной лабораторной работе. В начале занятия преподаватель проверяет выполнение студентом домашнего задания и наличие заготовки отчета по данной лабораторной работе в его рабочей тетради.

К выполненной работе прилагаются необходимые схемы, эскизы, тексты и результаты проектирования, протоколы работы с программным комплексом и другие материалы согласно указаниям по оформлению отчета.

1.2. Домашнее задание и методические указания по его выполнению

При выполнении домашнего задания студент должен ознакомиться с основными понятиями цифровой схемотехники и цифровой обработки сигналов, изучить основные модели и система параметров логических элементов. Для этого необходимо воспользоваться лекциями по курсу и литературой [1, С. 7-21 ].

На рисунке 1 представлена схема маршрута проектирования цифровых устройств.

Основные этапы маршрута проектирования цифровых устройств:

1. RTL-кодирование – разработка функционального описания блока на языках VHDL или Verilog - может выполняться как в ручном, так и в автоматизированном режимах.

2. Для моделирования используется тот же набор программных средств, что и при RTL-кодировании.

3. Логический синтез – процесс автоматизированного создания электрической (логической) схемы на базе RTL-описания и библиотек элементов логического уровня от производителя.

4. Вентильная верификация обычно сводится к статическому временному анализу списка цепей, полученному в результате логического синтеза. В отдельных случаях, когда размерность списка цепей невелика, можно выполнять моделирование на вентильном уровне.

5. Целью физического проектирования является разработка топологии кристалла интегральной микросхемы при выполнении проектных норм и требований спецификации.

6. Основная цель функциональной верификации – комплексная отладка функциональной модели совместно с программным обеспечением. На выходе маршрута должны быть представлены: список цепей (Verilog или VHDL), производственные тесты или топология.

Рис. 1. Маршрут проектирования цифровых устройств

Полученный в результате работы RTL код предназначен для дальнейшего программирования.

Языки высокого уровня являются универсальными, так как не связаны с аппаратными платформами. Среди них наиболее распространены языки VHDL и Verilog. Остановимся более подробно на языке VHDL. Язык VHDL является проблемно-ориентированным языком, его основные прикладные аспекты связаны с использованием в качестве рабочего инструмента для задач описания структуры или поведения широкого класса цифровых устройств. Описания могут использоваться для синтеза или моделирования таких систем. В соответствии с назначением, язык приспособлен для описания систем как с точки зрения их структурной организации (из модулей с известным поведением), так и с точки зрения поведения либо системы в целом, либо всех ее составных частей. Наибольшие ограничения на набор допустимых (относительно стандарта) операторов языка имеют компиляторы для синтеза спроектированных устройств, значительно меньше ограничений существует у систем моделирования.

Описание проекта на языке VHDL имеет типовую структуру. В его начале указываются библиотеки функциональных элементов, которыми может пользоваться САПР. Проблемно-ориентированными и поэтому наиболее важными средствами и понятиями языка VHDL являются:

средства описания иерархии проекта для описания структуры или поведения отдельных объектов проекта;

средства задания и описания параллелизма для выполняемых действий и операторов;

понятие сигнала для физических объектов, имеющих временное измерение для своих значений и средства для работы с ними.

Иерархическое построение описания системы в языке VHDL является развитием традиционного иерархического подхода и отличается тем, что распространяется не только на описание поведения, но и на описание структуры системы. Архитектурное тело (Architecture Body) – описывает поведение объекта или его структуру. Внутри архитектурного тела может быть и смесь структурного описания с поведенческим. Специальные синтаксические конструкции могут описывать интерфейс структурной компоненты объектов (component ... port), соединение компонентов между собой (port map, generic map), создание фрагмента структуры (for ... generate и if... generate) или конкретизации конфигурации (for ... use). Tо, что описанию архитектуры предшествует описание интерфейса объекта (Entity), не является существенным отличием языка VHDL и аналогично (в определенном смысле) описанию прототипа в языке СИ [51, 86, 91].

Наиболее важным свойством языка VHDL является понятие параллелизма выполнения действий. Параллелизм начинается с введения понятий процесса (Process) и охраняемого блока (Block) и распространяется при определенных условиях на такие традиционно последовательные операторы, как вызов процедуры и оператор присвоения.

Ещё одной важнейшей особенностью языка VHDL является введение физического типа данных. Понятие сигнала (Signal) отражает основные свойства реальных входных и выходных данных проекта.

Рассмотрим структуру и организацию ОЗУ статического типа. За основу примем структуру ОЗУ на 4К слова с разрядностью 64 бит, которая затем будет является элементом структуры ОЗУ на 256К слов и более.

Двухкоординатная выборка реализуется при помощи двух дешифраторов адреса выбора столбцов DCy и строк DCx матрицы запоминающих ячеек (ЗЯ), на пересечении которых и расположена искомая ЗЯ (см. рис. 2).

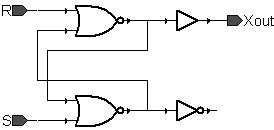

Запоминающий элемент (ЗЭ) ОЗУ предназначен для хранения 1бита информации, а ЗЯ – 1 слова. Слово в данном случае примем 64-разрядное, соответсвенно и разрядность ЗЯ – 64 бит. Запоминающий элемент представляет собой RS-триггер, в данном случае на элементах ИЛИ-НЕ (см. рис. 3).

Рис. 2. Структура ЗУ типа 3D

Рис. 3. Схема RS-триггера

Триггер имеет два входа – установки в единицу (S) и установки в ноль (R), два выхода, но в данном случае необходим один Xout.

Схема запоминающей ячейки на одно 64-разрядное слово представлена на рис. 4. Рассмотрим далее сигналы и блоки данной ЗЯ.

Ax, Ay – адресные входы соответственно дешифраторов сторок и столбцов матрицы;

CS – сигнал разрешающий или запрещающий работу ЗЯ;

RW – сигнал чтение-запись ЗЯ (при подаче 1 – чтение, при 0- запись);

RESET – сброс, установка ЗЯ в ноль;

Xin, Xout – соответственно входная и выходная 64-разрядная шина данных;

Slovo – блок предназначенный для хранения 64-разрядного слова, состоящий из 64 RS-триггеров. Сигнала S и Xout которых объединены соответствующими шинами данных.

Keysin1 – набор элементов И, предназначенных для реализации условия выполнения команд записи слова.

Keysin – аналогичен Keysin1 за исключением того, что при подаче на вход clock логического нуля ЗЯ переводится в высокоимпедансное состояние.

Рис. 4. Запоминающая ячейка

Запись в ЗЯ осуществляется при наличии единиц на Ax, Ay и CS. Поступившее 64-разрядное слово после срабатывания блока keysin1 заносится в блок slovo. В данном блоке за каждый разряд отвечает один RS-триггер. Слово здесь продолжает храниться до прихода следующей команды.

Чтение осуществляется при наличии единицы на RW, что приводит к срабатыванию блока keysin и прохождению слова на выходную шину данных Xout.

Обнуление ЗЯ происходит при подачи на CS нуля, а на RESET единицы.

Вопросы к домашнему заданию

1.3.1. Дать определение идеализованного логического элемента.

1.3.2. Перечислить основные операции логических переменных, переислить существующие базисы.

1.3.3. Статические параметры логических элементов.

1.3.4. Пояснить как реализована двухкоординатная выборка структуры ОЗУ.

1.3.5. Пояснить как реализована запоминающая ячейка ОЗУ.

1.4. Лабораторное задание и методические указания по его выполнению

Проектирование ОЗУ начинается с разработки элементов памяти – запоминающих ячеек. Студенты должны построить и отладить модель запоминающей ячейки ОЗУ на логическом уровне, опираясь на пример приведенный в домашнем задании, в соответствии с данными варианта. Исходные данные вариантов приведены в приложении методических указаний.

1.5. Контрольные вопросы

1.5.1. Какова цель лабораторной работы?

1.5.2. В чем заключается лабораторное задание? Пояснить ход его выполнения.

1.5.3. Какие данные являлись исходными для выполнения работы?

1.5.4. Пояснить работу полученной модели запоминающей ячейки на примере поступления на вход одного бита информации.

1.5.5. Сформулируйте выводы по данной лабораторной работе.